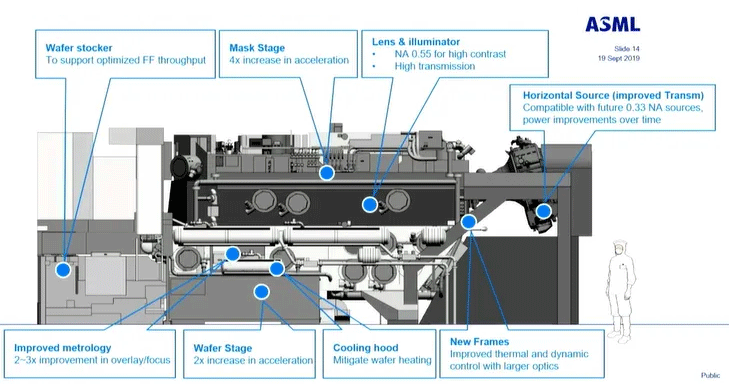

Futuro escáner ASML con alta apertura numérica 0.55 (EUV de alta NA) por valor de alrededor de $ 300 millones Fuente: Presentación de ASML

La empresa holandesa ASML es un monopolio en el equipo para fotolitografía en ultravioleta profundo (EUV) con un margen de liderazgo tecnológico durante varios años por delante de competidores ... Por lo tanto, el retraso en la próxima generación de escáneres no afectará las ganancias de la compañía, dicen las fuentes de Seeking Alpha. Por el contrario, ASML hará aún más dinero vendiendo equipos de generación actual.

Algunos expertos creen que en la situación actual no hay tiempo para actualizaciones. El déficit es tan fuerte que algunos fabricantes, por el contrario, están retomando la producción de microcircuitos de la anterior. generaciones anteriormente discontinuadas.

Pero esta es la situación del mercado. En el futuro, TSMC y Samsung, por supuesto, planean mejorar el proceso tecnológico. La única pregunta era: implementar los siguientes proyectos en el equipo actual con su actualización a multipatrón (varias operaciones secuenciales de litografía y grabado a través de varias fotomáscaras con una disminución de nodos a 5/3 nm) - o esperar un nuevo sistema EUV con una plantilla a 3/2 nm.

El instrumento actual para la litografía ultravioleta profunda es ASML NXE: 3400C, y el escáner de litografía EUV de alta NA de próxima generación será ASML EXE: 5000. Estará equipado con ópticas de 0.55 NA completamente nuevas, lo que reducirá significativamente el tamaño de los elementos de grabado en la oblea de silicio.

La forma en que se calculan la apertura numérica y la resolución son dos de las principales características de un escáner. Fuente: Presentación en ASML Ruta

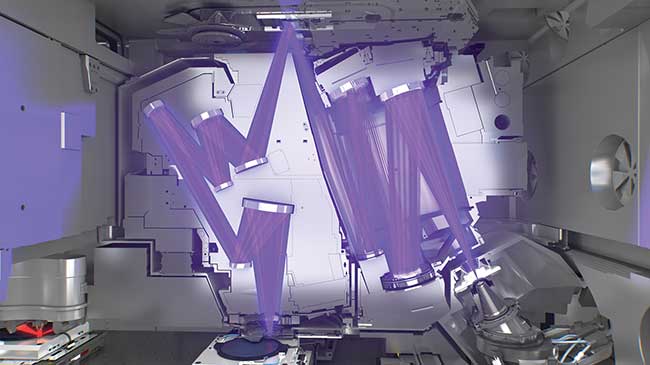

del pulso de luz desde el láser (abajo a la derecha) hasta el dispositivo de iluminación, máscara con topología de cristal a través de óptica de proyección sobre oblea de silicio en un escáner ASML real.

Ahora el problema está "resuelto". La transición a nuevos equipos se pospone hasta 2025 o 2026. Estos sistemas resultaron ser demasiado complicados y costosos en producción, escribeBuscando Alfa. Como recordatorio, los vehículos de 180 toneladas, del tamaño de un autobús de dos pisos, son en sí mismos testimonio de la compleja logística de la industria electrónica. Los componentes son fabricados por unos 5.000 proveedores. Por ejemplo, el alemán Carl Zeiss produce lentes. VDL holandés: manipuladores robóticos que introducen placas en una máquina. Las fuentes de luz son fabricadas por la empresa estadounidense Cymer, comprada por ASML en 2013.

Según se informa, un escáner EUV de alta NA costará alrededor de $ 300 millones (los escáneres ASML de la generación actual cuestan alrededor de $ 180 millones cada uno). Quizás se convierta en el aparato industrial más caro de la economía mundial.

No hay absolutamente nada de malo en la latencia de los escáneres ASML EXE: 5000. Los microcircuitos de 3 nm podrían producirse en equipos nuevos, pero ahora, tal vez, se hagan en escáneres antiguos, en varias pasadas y utilizando otras arquitecturas. Y los escáneres de próxima generación utilizarán chips de 2 nm.

El equipo EUV actual para chips de 7 y 5 nm utiliza un sistema óptico de 0.33 NA y una o dos exposiciones litográficas. En un momento dado, el doble pase parecía fácil. Ahora existe una creciente preocupación de que el patrón dual EUV es demasiado complejo y costoso para muchos dispositivos. Y a 3 nm, es posible que se requiera un triple paso, lo que es aún más difícil.

Fotolitografía en ultravioleta profundo

A lo largo de los años, los fabricantes de chips han reducido sistemáticamente el tamaño de los nodos en un 30% por generación, reduciendo así el costo de cada transistor. A su vez, esto hizo posible producir procesadores más potentes. El ciclo marcaba constantemente cada 18 meses.

La fabricación fue sencilla hasta la marca de 20 nm cuando los transistores planos golpearon la pared. A partir de 2011, los fabricantes de chips cambiaron a transistores de puerta vertical (FinFET) de 22 nm y 16/14 nm.

Los FinFET son más rápidos y requieren menos energía, pero son difíciles y costosos de fabricar. Por lo tanto, el tiempo de transición a nuevos nodos aumentó de 18 meses a 2,5 años.

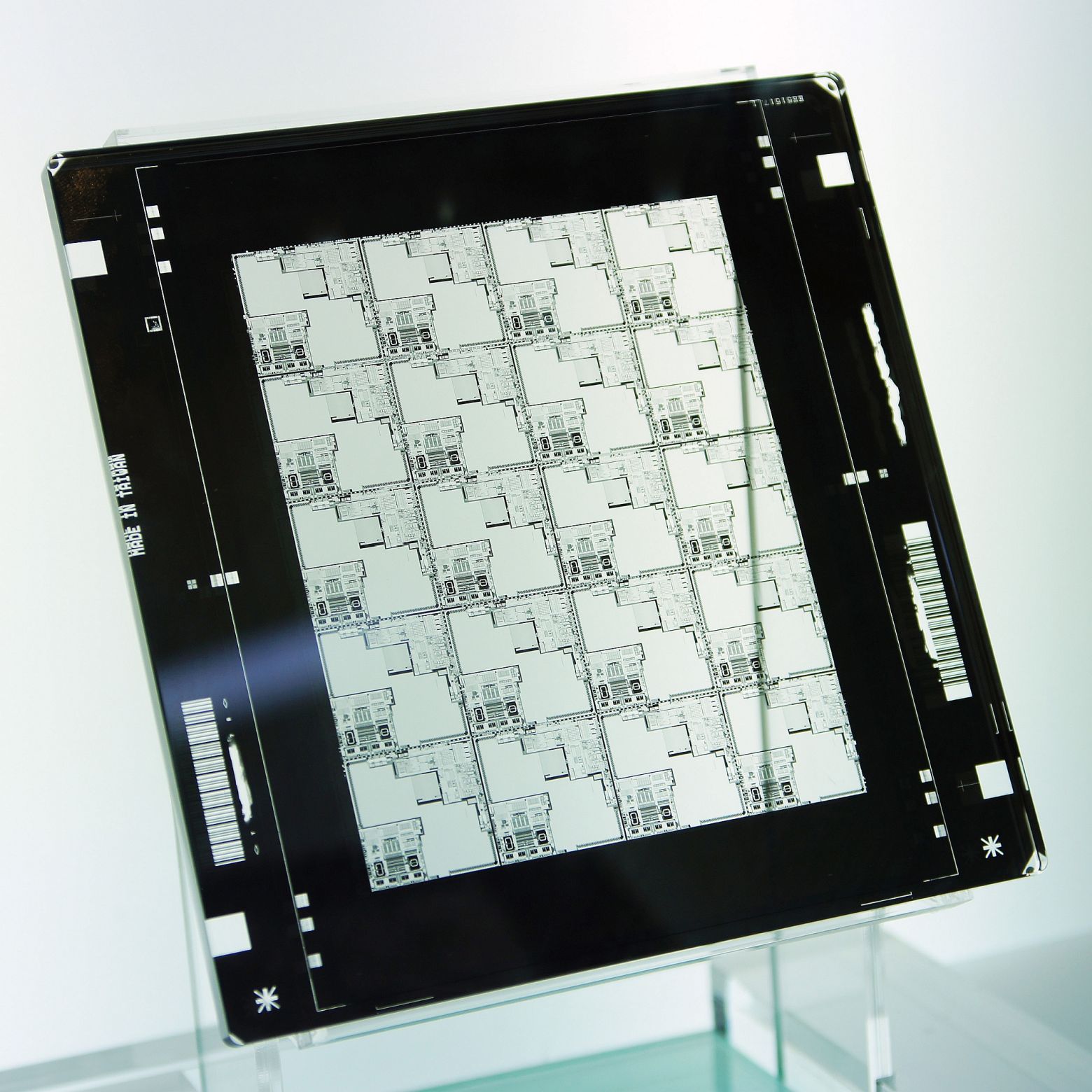

La litografía también enfrentó dificultades. El proceso de litografía comienza con una fotomáscara.

Fotomáscara

En fábrica, la fotomáscara se coloca en el escáner. Proyecta luz a través de la máscara sobre el plato, creando patrones en él, que luego se graban con ácido. Este es un proceso simple con un tamaño de paso de 28 nm, pero ya a partir de 20 nm, las partes se vuelven demasiado densas, lo que dificulta la impresión de elementos individuales en la oblea.

Fotomáscara realista con corrección óptica de proximidad. Autor: LithoGuy

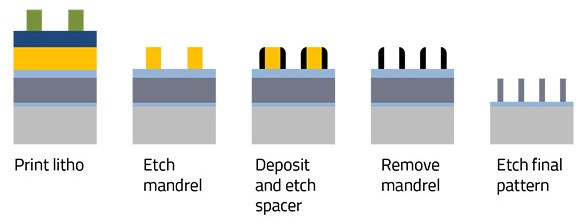

Por lo tanto, los fabricantes de chips cambiaron al multipatrón, donde el diseño original se divide en dos o más fotomáscaras "dispersas". Para aplicar estos elementos a la oblea, los fabricantes de chips utilizan una variedad de diseños de proceso en la fábrica, incluido el espaciador autoalineado y el patrón doble.

Los espaciadores autoalineables evitan que la máscara se mueva. Fuente: Lam Research

La reticulación doble aumenta la densidad. Fuente: Lam Research

El escáner ASML más avanzado NXE: 3400C utiliza una longitud de onda de 13,5 nm y un sistema óptico de 0,33 NA. La fuente de alimentación de 246 vatios ofrece un rendimiento de 170 obleas por hora (WPH).

Samsung, TSMC e Intel se están moviendo gradualmente a nodos de tecnología de 7 y 5 nm utilizando escáneres ASML NXE: 3400C. Según la información disponible , en la tecnología de proceso de 7 nm, una pasada con un paso de 40 nm es suficiente, pero ya en chips de 5 nm, el mismo TSMC usa un paso de 30 nm, que está cerca del límite físico en esta apertura. .

¿Qué es alta NA?

Aunque la reticulación doble todavía es posible para 5 o incluso 3 nm, este es el límite para los semiconductores de puerta vertical. A continuación, debe dominar los transistores de nanohojas (Nanosheet FET).

Transistores de nanohojas Los

nuevos escáneres ASML con alta apertura numérica (alta NA), que permiten aumentar la resolución de imagen en una fotomáscara, son indispensables.

ASML anunció en la conferencia de informes de enero que estaba retrasando la implementación de la nueva versión de EUV durante al menos tres años. Anteriormente, se planeó dominar la tecnología para 2023, y ahora los planes se posponen hasta 2025 o 2026.

Según los expertos, se requieren una serie de mejoras tecnológicas para dominar la tecnología de proceso de alta NA. La industria está trabajando en ellos, pero hay varios factores desconocidos aquí.

En los últimos años, los fabricantes de chips han trabajado en paralelo en otras arquitecturas de empaquetado de chips (2.5D, 3D-IC, etc.) para escalar aún más los chips incluso en el caso de una latencia de alta NA.

Por cierto, el retraso actual de alta NA recuerda cómo la industria ha estado estancada en la litografía de inmersión de 193 nm durante mucho tiempo, lo que finalmente impulsó las ventas de equipos. Entonces, desde el punto de vista del negocio ASML, no hay ningún problema: la empresa ganará más dinero con la EUV de primera generación. También entró en el mercado con grandes retrasos y no pasó nada terrible.

La introducción de los escáneres ASML NXE: 3400C comenzó en 2020. De los tres principales fabricantes TSMC, Samsung e Intel, los dos primeros son líderes en el uso de los últimos equipos ASML para fotolitografía ultravioleta profunda, e Intel planea cambiar a la litografía EUV solo a fines de 2022.