Más recientemente, encontré una de las opciones para una placa de depuración con SoC Zynq XC7Z020. Después de buscar materiales en Internet, cómo hacer y tratar de incluir mi proyecto mínimo, descubrí que hay una serie de trampas. De esto es de lo que me gustaría hablar en el artículo. A quién le importa, bienvenido a cat.

¡Importante! Antes de comenzar la historia, me gustaría hacer una reserva por adelantado de que el objetivo principal que persigo al escribir este artículo es mostrar a los aficionados por dónde empezar cuando estudian los tableros de depuración basados en Zynq. No soy un desarrollador profesional de FPGA y SoC Zynq y puedo cometer errores en el uso de la terminología, no utilizar las formas más óptimas de resolver problemas, etc. Pero cualquier crítica constructiva y bien razonada es bienvenida. Bueno, vamos ...

¿Qué tipo de depuración es esta? Show-tell ...

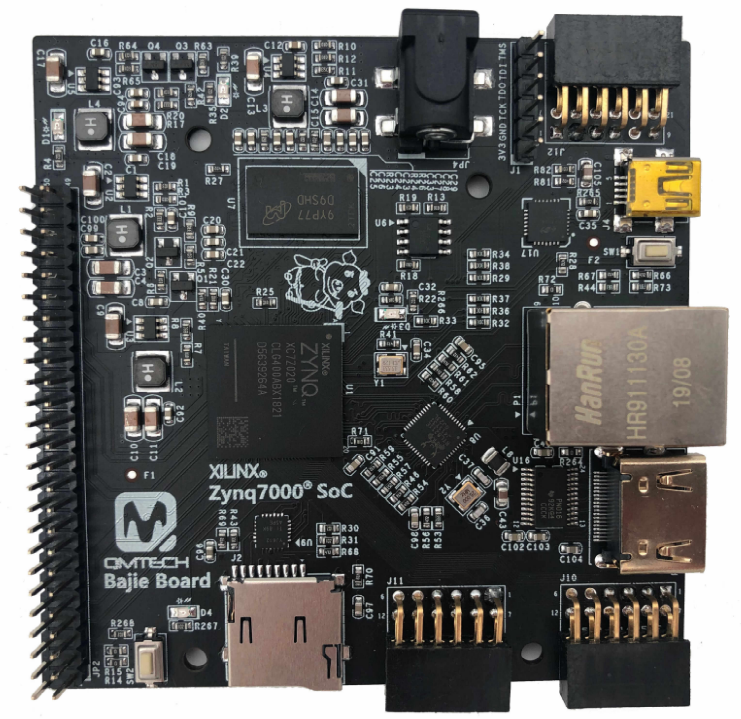

Durante mucho tiempo quise jugar con SoC Zynq, pero mis manos no podían llegar. Pero una vez más buscando en Google, vi que la depuración con Zynq a bordo, de QMTech, se vende por un precio completamente sensato, se llama Bajie Board. Debug está disponible en varios sabores con diferentes sabores de Zynq SoC. Elegí la versión XC7Z020 para mí y la ordené inmediatamente, después de un par de semanas ya la tenía en mis manos.

, . , 5/2, mini-USB microSD Flash- SanDisk 16 Linux. , , USB-, Putty mini- Embedded Linux. Linux Zynq, , , ...

, -:

SoC: XC7Z020-1CLG400C

(datasheet:https://www.xilinx.com/support/documentation/data_sheets/ds190-Zynq-7000-Overview.pdf);

33,333 ;

DDR3 512 Micron, MT41K256M16TW-107:P;

micro SD;

FPGA TPS563201 ( 4.5V 17V, 3A);

50- Digilent PMOD , , 2,54 . ( , );

(PS);

RGMII Ethernet- Realtek RTL8211E-VL, PS;

, (PL) (PS);

HDMI- TI TPD12S016;

JTAG-;

.

, , - JTAG-. .

, Xilinx Vivado Xilinx SDK. , , Vivado . Xilinx SDK ( Vitis) .

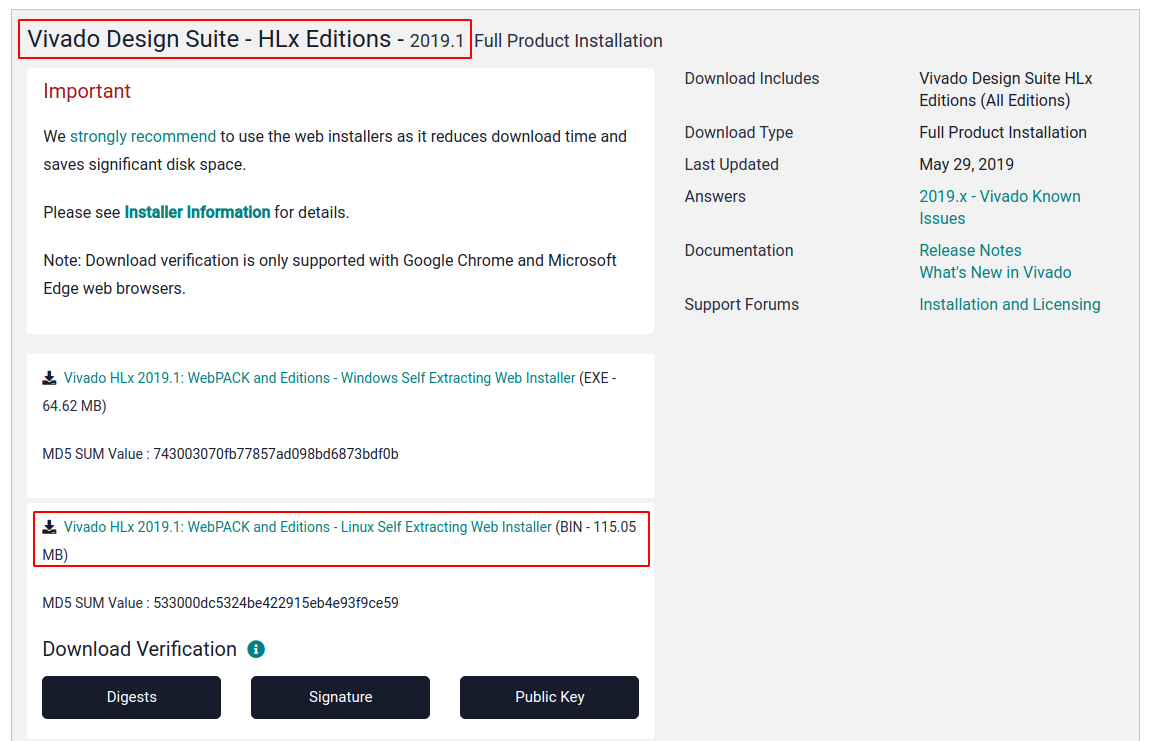

YouTube Vivado 2019.1 ( - , Xilinx SDK) - , 2020.2.

Xilinx Zynq - Xilinx, . , , Vivado - 2020.2, 2020.3 .. Versal SoC, Zynq.

, .. Linux - Vivado Archive - 2019.1 Vivado HLx 2019.1: WebPACK and Editions - Linux Self Extracting Web Installer Vivado Design Suite - HLx Editions - 2019.1. Windows - Windows Self Extracting Web Installer.

, :

chmod +x ~/Downloads/Xilinx_Vivado_SDK_Web_2019.1_0524_1430_Lin64.bin ~/Downloads/Xilinx_Vivado_SDK_Web_2019.1_0524_1430_Lin64.bin

.

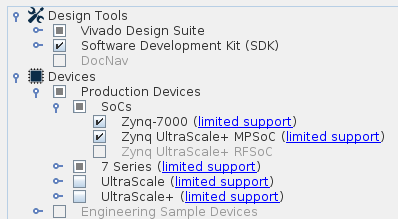

, ;

;

Vivado HL WebPACK;

, SoC Zynq .

16 -, .

Vivado JTAG-. Linux :

cd Xilinx2019.1/Vivado/2019.1/data/xicom/cable_drivers/lin64/install_script/install_drivers/

sudo ./install_drivers

6 JTAG- . :

cd ~/Xilinx2019.1/Vivado/2019.1/bin

./xsdb

xsdb% connect -host localhost

xsdb% jtag targets

1 Platform Cable USB 13724327082b01

2 arm_dap (idcode 4ba00477 irlen 4)

3 xc7z020 (idcode 23727093 irlen 6 fpga)

.

Hello, world “ ”

LED- .

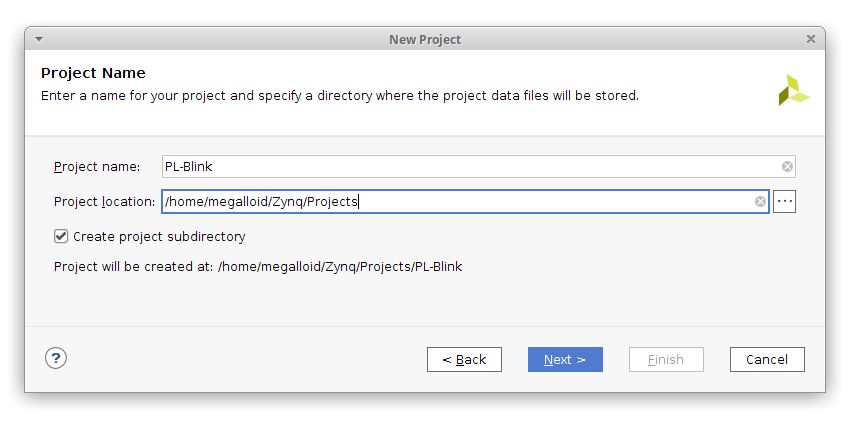

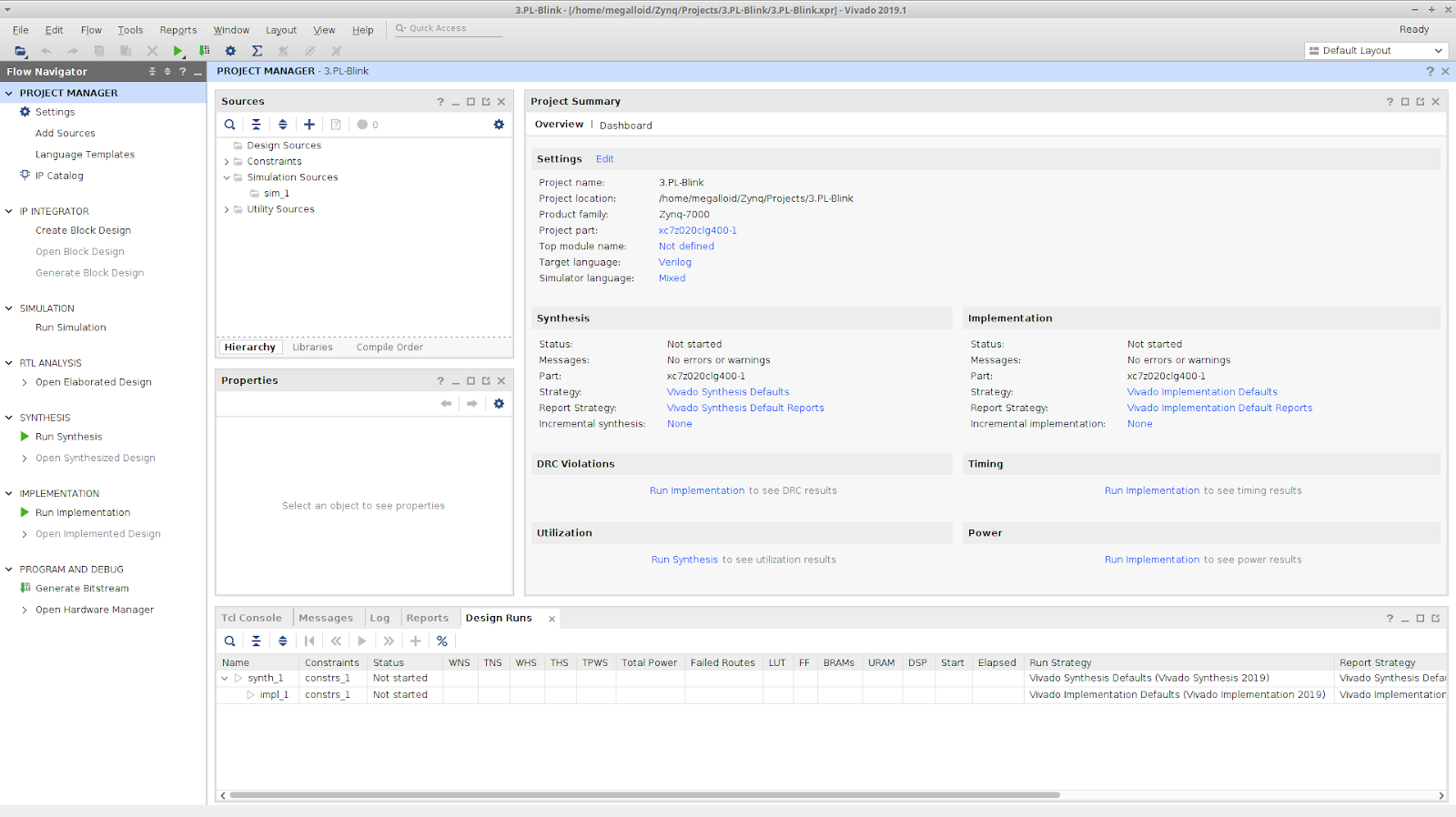

Vivado . File - Project - New…

, Next > PL-Blink.

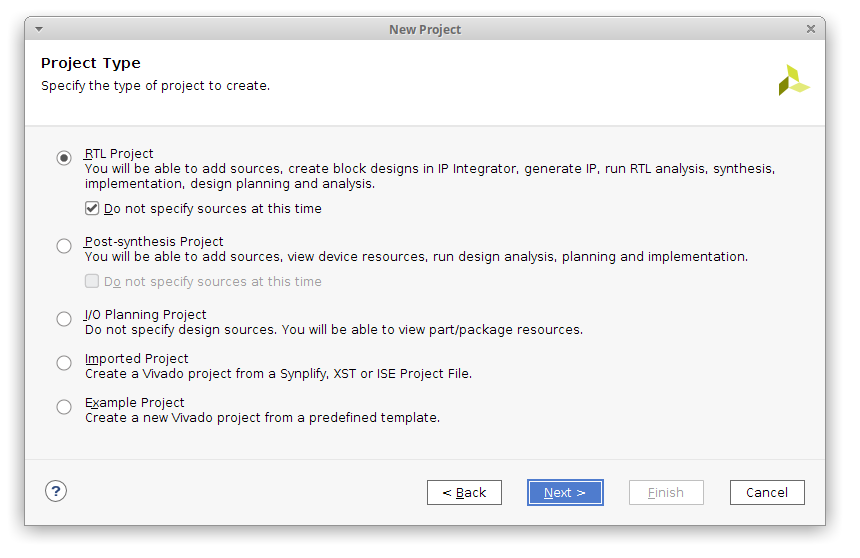

RTL Project Do not specify sources at this time.

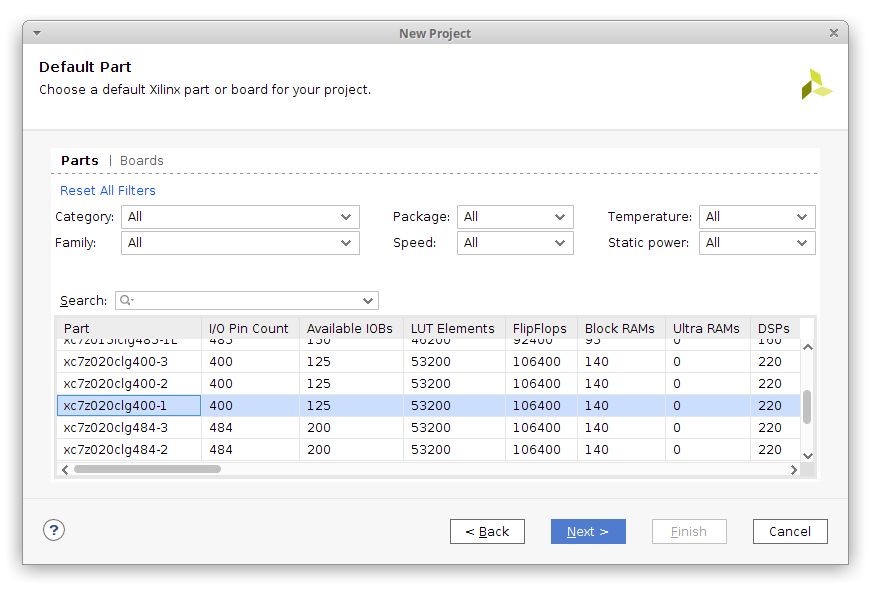

xc7z020clg400-1.

Finish.

Vivado !

, , , =)

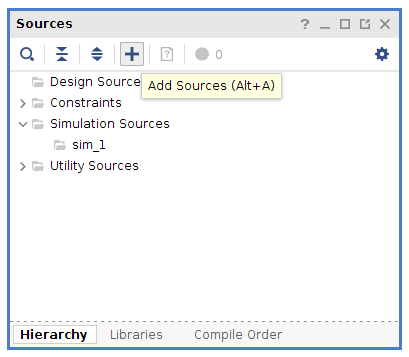

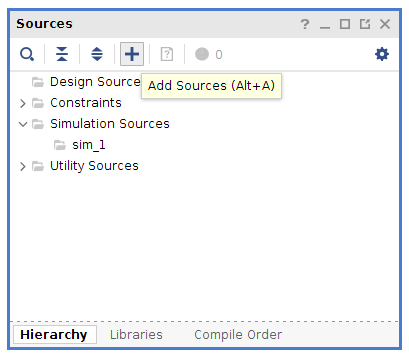

Sources Add Sources.

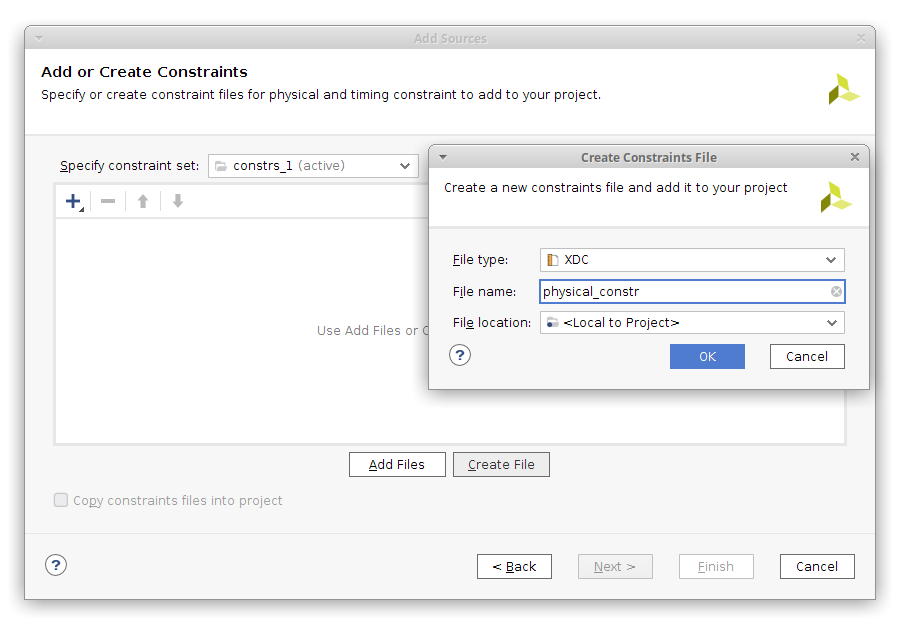

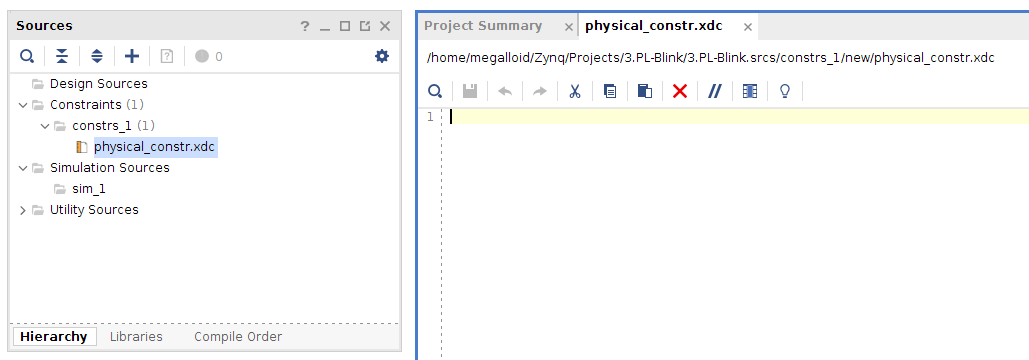

Add or create constraints.

Create file physical_constr. .

Finish Soures :

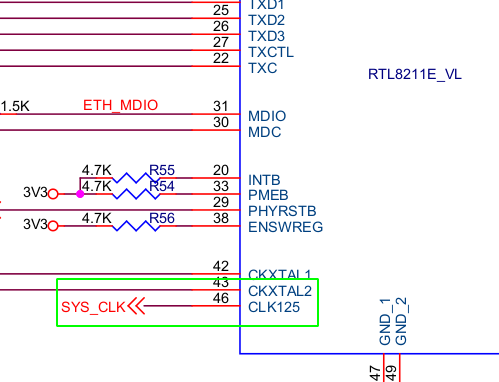

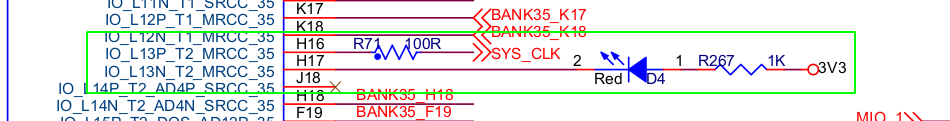

, , . , , Ethernet- RTL8211E-VL PLL, 125 H16 (IO_L13P_T2_MRCC_35). ? =)

, .

, , H17 (IO_L13N_T2_MRCC_35) , .

. constraints- :

# User LED and Clock

set_property IOSTANDARD LVCMOS33 [get_ports led_h17_d4]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN H17 [get_ports led_h17_d4]

set_property PACKAGE_PIN H16 [get_ports sys_clk]

, , , , .

, get_ports ( ). , Verilog-.

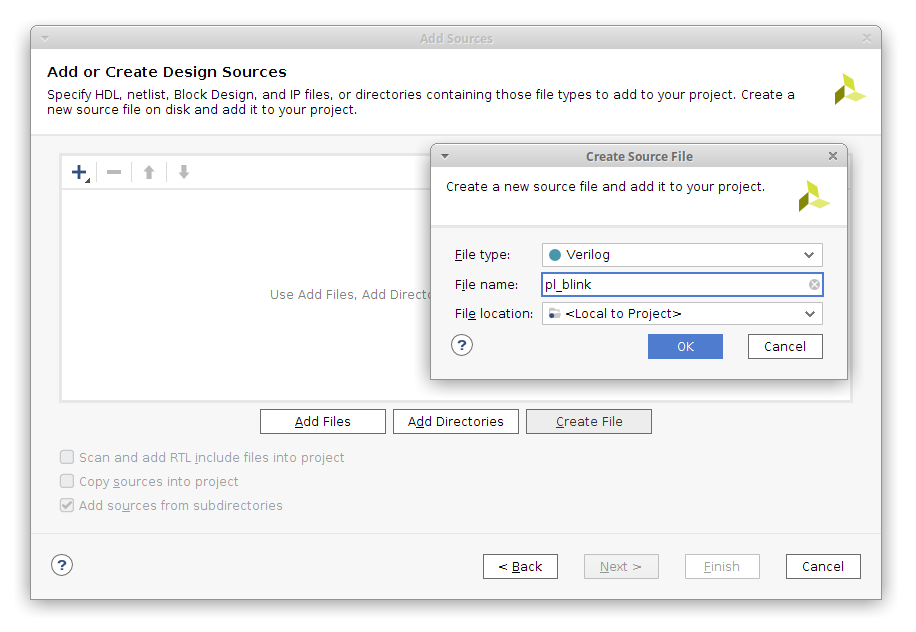

Design Source. Sources Add Sources.

Add or create design sources. Create File, , Verilog. Finish.

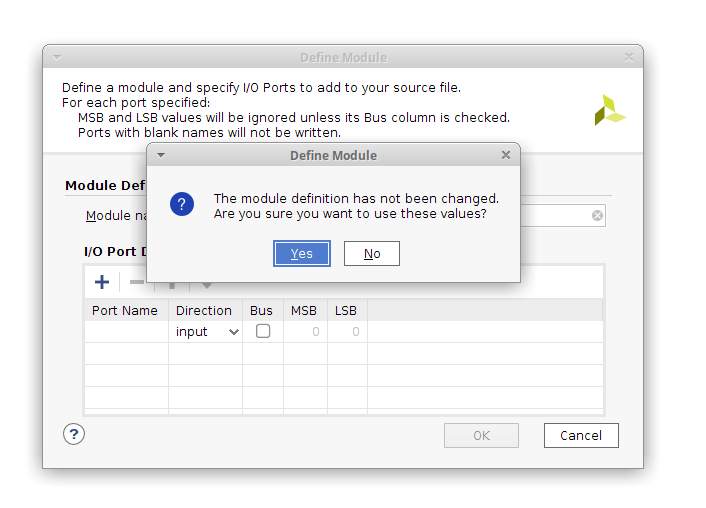

Yes.

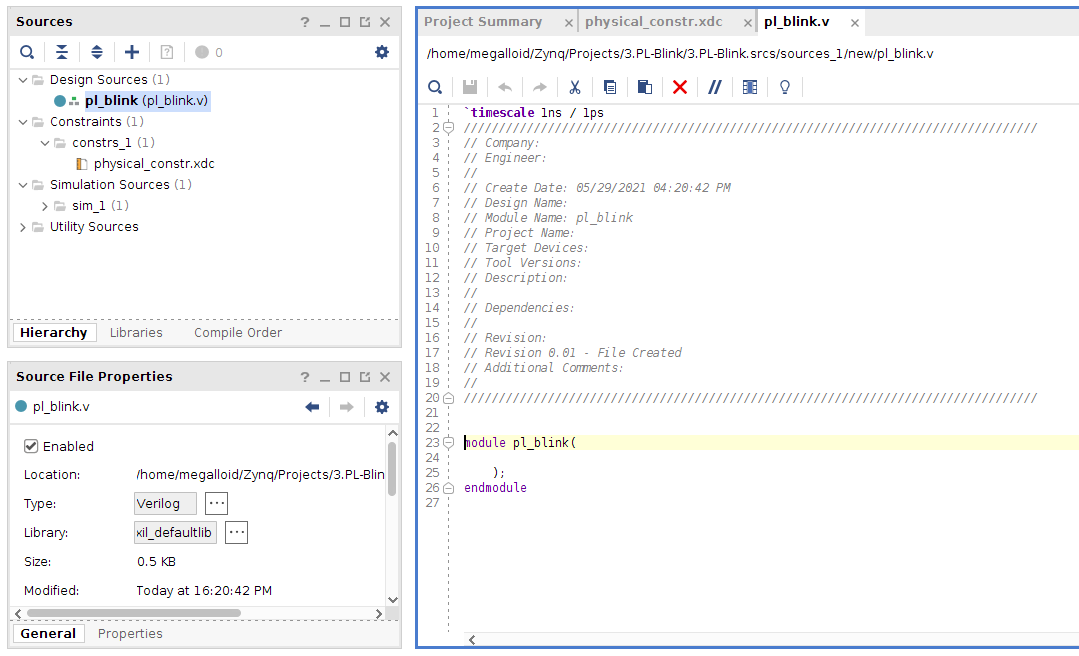

:

Verilog- :

// , Verilog.

// , .

`timescale 1ns / 1ps

// - ( ++)

module pl_blink(input sys_clk, output led_h17_d4);

//

reg r_led;

// ,

reg [31:0] counter;

//

initial begin

counter <= 32'b0; //

r_led <= 1'b0; //

end

// ,

always@(posedge sys_clk)

begin

counter <= counter + 1'b1; //

if(counter > 12000000) //

begin

r_led <= !r_led; //

counter <= 32'b0; //

end

end

assign led_h17_d4 = r_led; // ()

endmodule

Ctrl + S . , . - , Zynq .

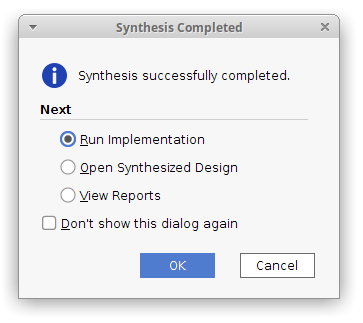

Run Synthesis . , :

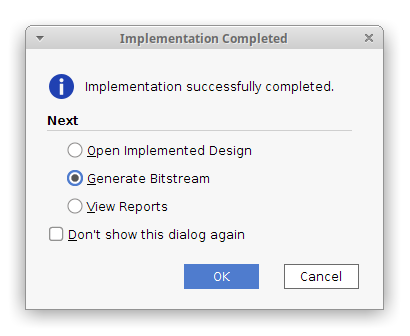

Run implementation . Generate Bitstream :

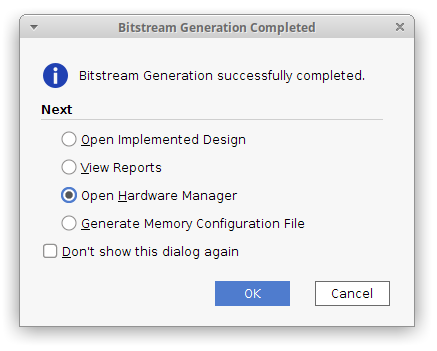

, , Open Hardware Manager :

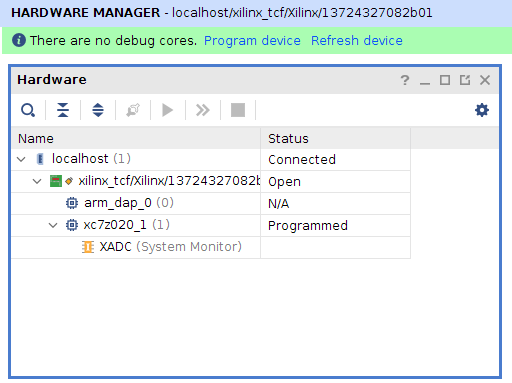

Hardware Manager Auto connect, :

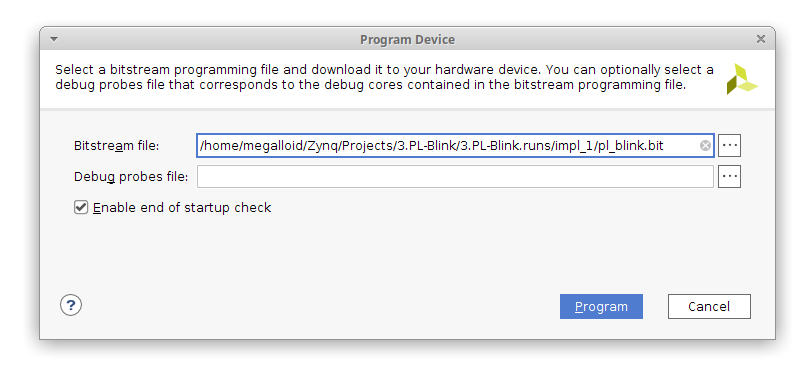

En el menú de la izquierda o haciendo clic con el botón derecho en xc7z020_1 en el menú Hardware , haga clic en el elemento Programar dispositivo .

En la siguiente ventana, asegúrese de que la ruta al archivo de flujo de bits esté especificada correctamente y haga clic en el botón Programa.

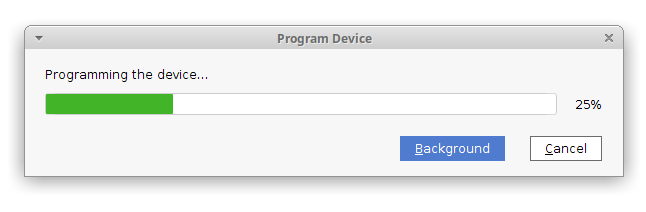

El programa está subido a nuestro tablero ...

Y después de un momento, el LED D2 en la placa se enciende, lo que nos informa que “FPGA DONE” y en el otro extremo de la placa vemos un LED parpadeando alegremente. =)

En general, la tarea se puede considerar completada. Creo que a medida que domine el lenguaje Verilog y resuelva cualquier problema nuevo con esta placa, podré complacerlos nuevamente.