IBM anunció el desarrollo de una tecnología de proceso de 2 nm.

Que se anunció:

- 2 nm.

- 50 mil millones de transistores en un área del tamaño de un clavo. Más tarde aclararon, en un área de 150 mm cuadrados, es decir, 333 millones de transistores por milímetro cuadrado (

- MTx / mm 2 ).

- El paso de la puerta del transistor (Contacted Poly Pitch, CPP) es de 44 nm, la longitud de la puerta es de 12 nm.

- (Gate All Around, GAA). – , IBM (horizontal nanosheets, HNS).

- HNS .

- 45% 75% 7 .

- (EUV) HNS 15 70 . , SRAM.

- 5 .

¿Es esta realmente una tecnología de proceso de 2 nm? Hoy TSMC es líder en la producción de chips. Trazamos la relación entre los nombres de los procesos TSMC y la densidad del transistor aproximando la curva con un coeficiente de determinación de 0,99.

De 28 nm a 5 nm, las cifras reales se utilizan de acuerdo con IC Knowledge y TechInsights. Las cifras de 3 nm se basan en los comunicados de prensa de TSMC. 2 nm y 1,5 nm es nuestra extrapolación.

Con el gráfico, puede convertir la densidad de transistores en una tecnología de proceso TSMC equivalente (nodo equivalente TSMC o TEN). Obtenemos 2,9 nm para 333 MTx / mm 2 . Desde nuestro punto de vista, resulta que se trata de una tecnología de proceso de 3 nm, no de 2 nm.

Para comparar con más detalle el anuncio de IBM con los anuncios anteriores de la tecnología de proceso de 3nm y el proceso de 2nm propuesto, se deben hacer varias suposiciones.

- Se sabe por el anuncio que el CPP es de 44 nm.

- Suponga que la producción está utilizando la tecnología de colocación de transistores más ajustada, Single Diffusion Break (SDB).

- Según la foto recortada del anuncio, no se utiliza la tecnología Buried Power Rails (BPR). El BPR es necesario para reducir el tamaño de la pista HNS a 5.0, así que supongamos que este valor es 6.0 en este proceso.

- Para lograr una densidad de 333 MTx / mm 2 , el paso mínimo del metal tendría que ser de 18 nm, un valor muy agresivo que probablemente requeriría fotolitografía de múltiples matrices EUV.

IBM de 2 nm frente a la tecnología de proceso de 3 nm existente

La siguiente tabla compara los diseños de IBM con nuestras estimaciones de proceso de 3 nm de Samsung y TSMC. Sabemos que Samsung también está trabajando con HNS, y TSMC se ha decidido por FinFET de 3 nm. Samsung y TSMC también anunciaron un aumento de 3 nm en la densidad de transistores para su tecnología de proceso en comparación con 5 nm. Por lo tanto, conocemos la densidad de los transistores de las tres compañías y podemos calcular las DIEZ para todas. TEN de IBM es 2,9; se puede ver que Samsung tiene 4.7 y TSMC tiene 3.0. Nuevamente, resulta que 2 nm de IBM es más similar a 3 nm de TSMC, mientras que Samsung se está quedando atrás.

Los parámetros indicativos necesarios para alcanzar las densidades anunciadas se resaltan en rojo, asumiendo que todas las empresas están utilizando tecnología SDB. La altura de las pistas es la menor en TSMC, ya que sin BPR en FinFET este parámetro puede llegar a 5.0, sin embargo, para que el HNS tenga la misma altura, se debe utilizar BPR.

IBM de 2 nm frente a la tecnología de proceso de 2 nm existente

En la siguiente tabla, estimamos los valores de los parámetros para la tecnología de proceso de 2 nm de Samsung y TSMC. En nuestra extrapolación, asumimos que las empresas están utilizando BPR (la tecnología BPR aún no está madura, pero es probable que entre en funcionamiento cuando anuncien un proceso de 2 nm en 2023-2024). Supongamos también que las empresas adoptan la arquitectura de hoja de horquilla NHS (HNS FS) para lograr una altura de pista de 4,33. Las estimaciones de CPP y MPP se basan en las tendencias actuales en miniaturización de tecnología.

Rendimiento y consumo de energía

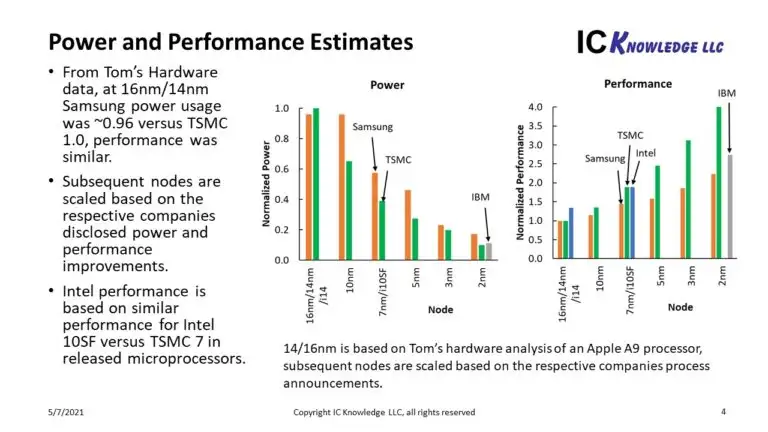

Este año ya hice conjeturas sobre el consumo de energía y el rendimiento de los dispositivos de Samsung y TSMC utilizando datos de rendimiento adicionales de Intel. La extrapolación se basa en garantías de empresas y en comparaciones del mundo real entre procesos de 14 nm y 16 nm.

Dado que IBM ha comparado las mejoras en el consumo de energía y el rendimiento con los procesos de fabricación avanzados de 7 nm, puedo trazar sus datos en los mismos gráficos.

Mediante el uso de HNS, IBM ha logrado ahorros de energía significativos, lo que hace que su proceso de 2 nm sea más eficiente que el proceso de 3 nm de Samsung y TSMC. Aunque, en nuestra opinión, cuando TSMC cambie a HNS a 2 nm, su consumo de energía no será inferior al de IBM. En términos de rendimiento, asumimos que el proceso de 3 nm de TSMC superará al proceso de 2 nm de IBM.

Por supuesto, todas estas son solo estimaciones basadas en una gran cantidad de suposiciones.

Conclusión

Después de analizar el anuncio de IBM, llegamos a la conclusión de que su tecnología de proceso de 2 nm es más similar a la tecnología de proceso de 3 nm de TSMC en términos de densidad de transistores, mientras que tiene los mejores indicadores de consumo de energía, pero inferior en velocidad. La declaración de IBM es impresionante; sin embargo, esta es solo una muestra de laboratorio, superando claramente los 3 nm de TSMC solo en consumo de energía. Al mismo tiempo, los primeros lotes riesgosos de dispositivos de 3 nm de TSMC aparecerán este año y los comerciales el próximo.

En nuestra opinión, TSMC mantendrá la ventaja en densidad, consumo de energía y velocidad de los dispositivos basados en la tecnología de proceso de 2 nm cuando entren en producción en 2023-2024.