Paradigma

Es muy importante enfatizar aquí que el código de la máquina debe verse, en una percepción subjetiva relativamente fluida, como un pseudocódigo en los campos de las tablas de volcado y, lo menos posible, dar la esotericidad de cualquier campo de bits.

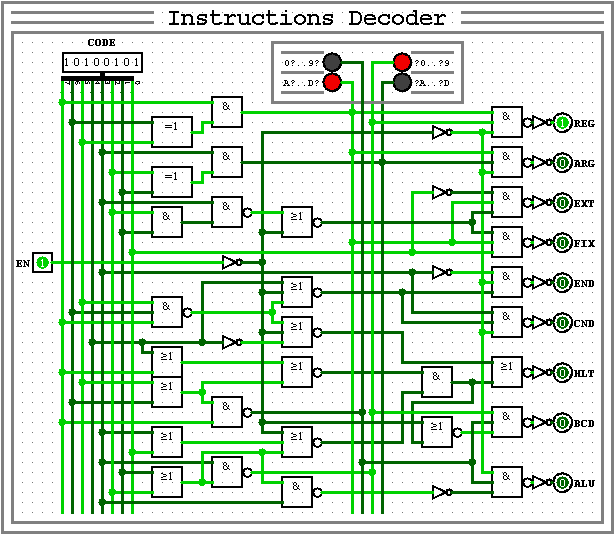

Decodificador de comandos

Uno de los elementos más importantes y clave de cualquier autómata es un dispositivo para decodificar exactamente esa acción en un momento determinado que el propio programador tenía en mente cuando compuso el orden de estos comandos en sus algoritmos.

Primero, es necesario hacer un boceto del decodificador Koda-Koyaaniskatsi en Logisim , utilizando las puertas lógicas más accesibles de la nomenclatura de la serie TTL que se está produciendo, para asegurar un fácil montaje del decodificador en microcircuitos reales.

Aquí presentamos una designación gráfica condicional para el decodificador, que es necesaria para garantizar la compacidad y claridad de todo el circuito de la máquina en el futuro, así como para verificar el correcto funcionamiento de la decodificación de los 256 códigos de instrucción.

Registros de prefijos atemporales

Cuando la prueba visual del rendimiento del decodificador fue bien y sin fallas visibles, llegó el momento de conectar los registros principales para almacenar los índices de RON activos, que son activados por los comandos del grupo REG como prefijos arquitectónicos.

Para asegurar el almacenamiento de vectores de enrutamiento de datos mediante instrucciones ALU y RAM, se agregan un registro más y dos multiplexores vinculados, con los cuales puede vincular registros arbitrarios de cualquier grupo como operandos de instrucción.

Por sí mismos, estos registros no están destinados a almacenar los resultados de los cálculos y desempeñan una especie de función como indicadores de los registros requeridos para proporcionar una interacción controlada en el programa entre todos los RON y / o la memoria disponibles.

Condición arquitectónica

Asegurar la interacción normal del software de todos los registros requiere un Archivo de Registro de dos puertos, que no está incluido en las bibliotecas Logisim, lo que nos obliga a buscar otras soluciones alternativas más o menos costosas. El clásico Koyaaniskatsi tiene un Archivo de Registro bastante complejo, que no se considera aquí como un ejemplo ilustrativo y requiere el desarrollo de una nueva solución para organizar un Archivo de Registro multiciclo con acceso lento. Dado que el esquema resultó ser de un ciclo, es bastante difícil organizar el Archivo de Registro en RAM aquí y se hace necesario construir un esquema de ciclos múltiples con muchos ciclos especiales reemplazándose entre sí en un orden estrictamente especificado.

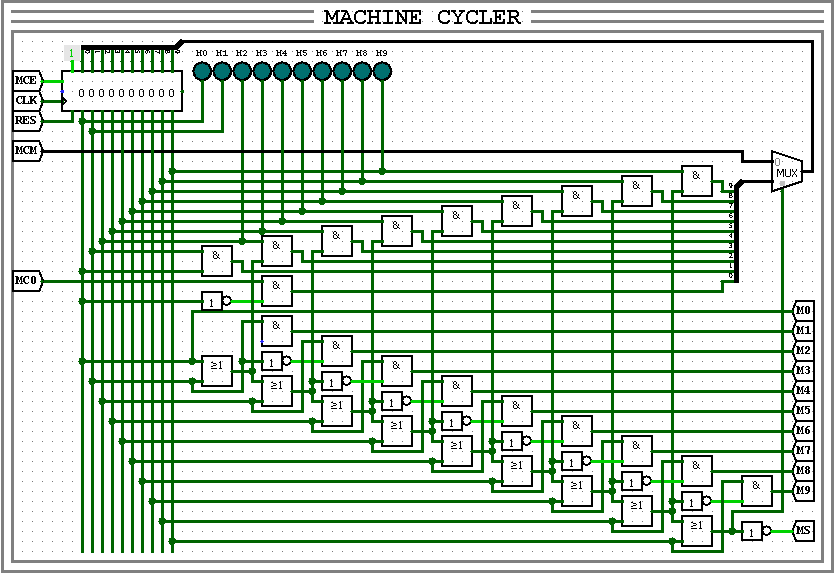

La expresión algorítmica del contador de ciclos se puede describir como "m & = m - 1" con desconexión secuencial de todos los bits activos del estado arquitectónico, donde en un momento determinado del ciclo de la máquina solo se activan los nodos clave del circuito.

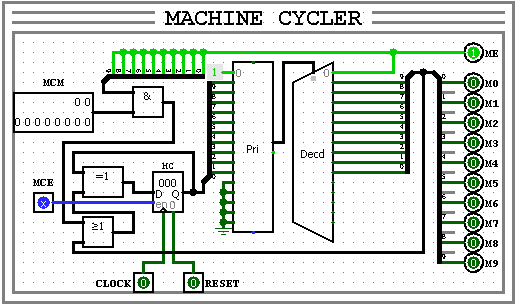

El prototipo ampliado al máximo del contador de ciclos de la máquina se puede representar en un boceto de un circuito similar, que es bastante difícil de entender la lógica de su funcionamiento.

Un boceto similar puede servir como la opción más óptima y universal:

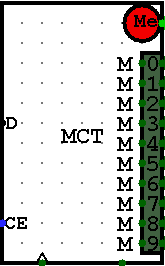

y para su uso en el esquema, la designación gráfica condicional puede ser la siguiente:

Con la ayuda de las puertas lógicas 3-OR, ahora es posible traducir la señal de cada uno de los comandos a la máscara de bits de los ciclos necesarios para la correcta ejecución del comando, durante todo el período de ejecución del cual el contador de comandos se suspenderá temporalmente.

Conclusión

Entonces, como puede ver, para al menos más o menos comenzar a comprender los matices de la construcción independiente de una máquina programable, solo necesitamos arreglárnoslas incluso con conocimientos básicos en los niveles de dibujar el esquema de una guirnalda de árbol de Navidad parpadeante. Aquí no se utilizaron deliberadamente materiales de referencia conocidos por todos, por lo que el proceso creativo fue más emocionante y libre de tendencias y tendencias globales, sin prestar atención a todos los posibles errores de cálculo o errores.

En la siguiente parte intentaré continuar con mi construcción paso a paso del "procesador akyn",

ya que el nuevo borrador casi me funciona, pero decidí volver a dibujarlo desde cero

y , al mismo tiempo, documentar todas las etapas clave ...