En 1974, Hewlett-Packard desarrolló un microprocesador para controlar varias funciones en sus productos, desde unidades de disquete hasta voltímetros. Este procesador simple no estaba a la altura de los microprocesadores estándar, ni siquiera admitía sumas o restas, por lo que se lo llamó "nanoprocesador". Las características clave del nanoprocesador eran el bajo costo y la alta velocidad de trabajo: en comparación con el moderno Motorola 6800 que cuesta $ 360, el nanoprocesador cuesta $ 15 y las operaciones de control son mucho más rápidas.

Aunque no tenía una operación de adición, el nanoprocesador podía (lentamente) agregar números aumentando o disminuyendo repetidamente (las operaciones que admitía). En otros casos, por ejemplo, con un voltímetro de Hewlett-Packard, se agregaron chips ALU (74LS181) al producto, que se agregaron rápidamente: se accedió a ellos como dispositivos de E / S. Naturalmente, siendo Turing completo, el nanoprocesador teóricamente podría hacer de todo, desde calcular funciones de punto flotante hasta lanzar un juego de Crysis; simplemente sería muy lento.

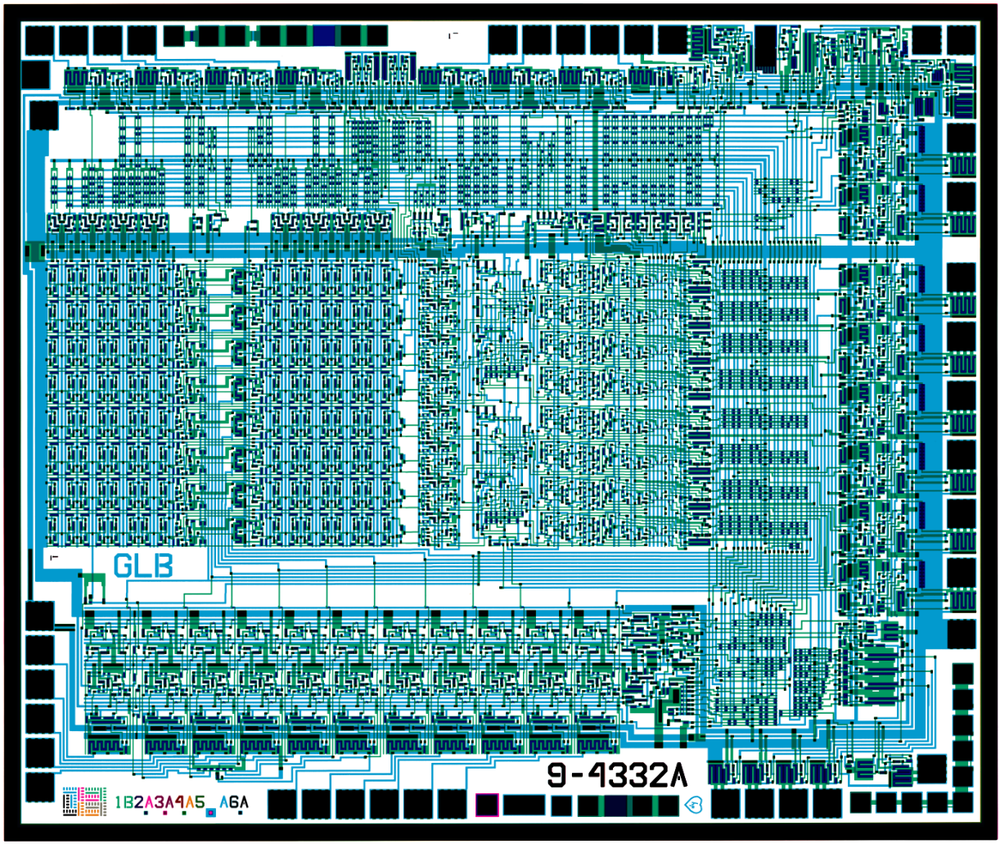

La fotomáscara del procesador se puede descargar desde el enlace (122 MB PSD).

HP Nanoprocessor, 1820-1691. , -2,5 , – . , .

En las décadas siguientes, el procesador permaneció desconocido hasta hace poco su desarrollador, Larry Bauer, compartió fotomáscaras y documentación para el chip con The CPU Shack. Allí escanearon las fotomáscaras y escribieron un artículo sobre Nanoprocesador. Después de que Antoine Berkovichi uniera las imágenes en una, escribí una reseña de Nanoprocessor basada en ella . Esta es la segunda parte del artículo, donde analizo algunos de los detalles del circuito del Nanoprocesador, haciendo ingeniería inversa basada en fotomáscaras. Los bloques funcionales de Nanoprocesador son interesantes de estudiar, ya que evita la implementación mínima de funciones necesarias, sin dejar de ser un microprocesador útil.

Dentro del nanoprocesador

Como la mayoría de los procesadores de esa época, el nanoprocesador es de 8 bits. Sin embargo, no admite memoria de acceso aleatorio y el código se ejecuta desde una ROM externa de 2KB. Tiene 16 registros de 8 bits, más que la mayoría de los procesadores y suficiente para compensar la falta de memoria de muchas aplicaciones. El Nanoprocesador tenía 48 instrucciones, significativamente menos que las 72 instrucciones del Motorola 6800. Sin embargo, el Nanoprocesador tenía un conjunto útil de operaciones de ajuste, borrado y verificación de bits de las que carecían otros procesadores de la época. También tenía varios comandos de E / S que admitían puertos de E / S y pines de E / S de propósito general, lo que facilitaba el control de otros dispositivos con él.

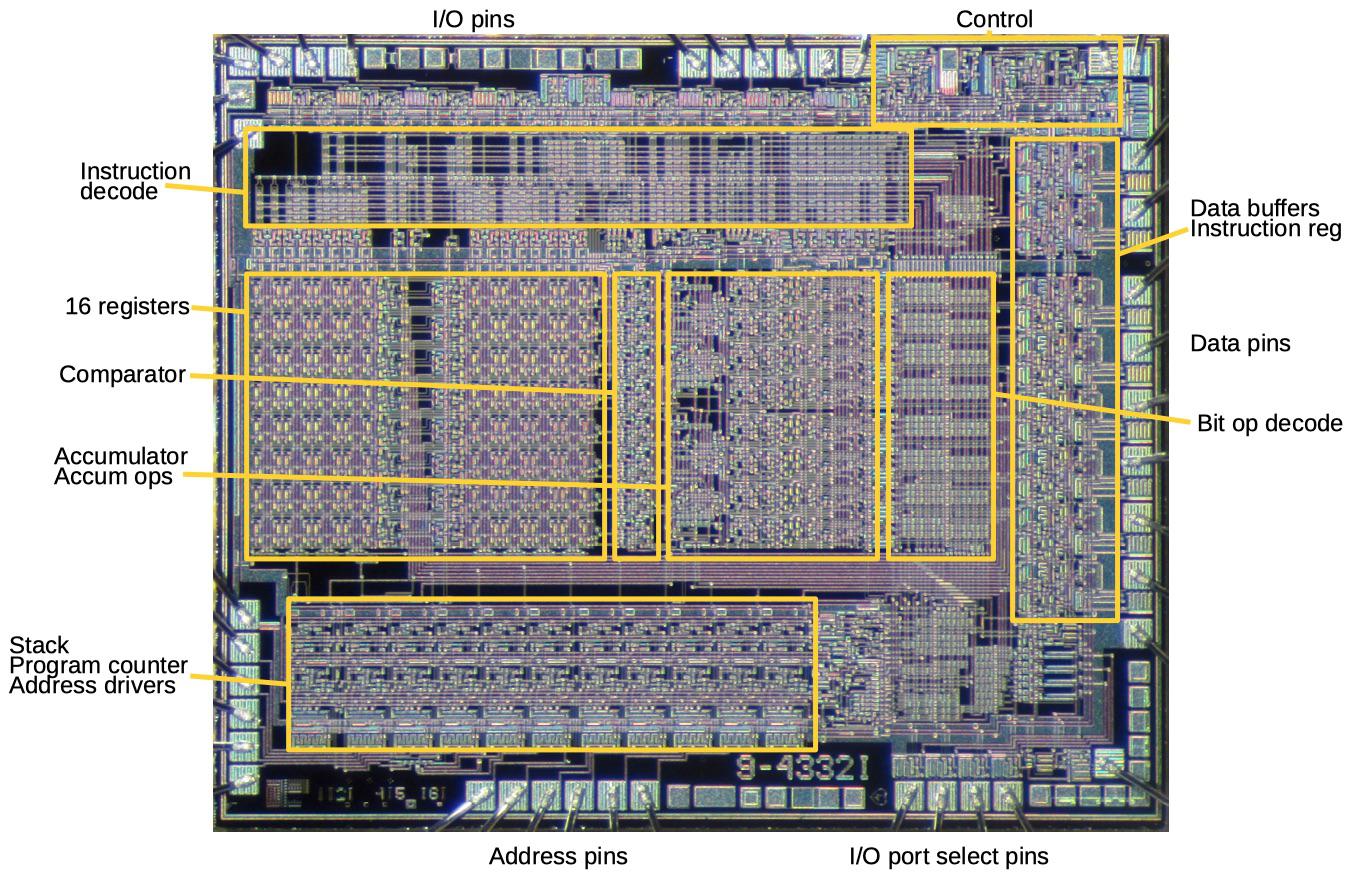

El nanoprocesador no tenía instrucciones para admitir el manejo de la memoria, ya que fue diseñado para operaciones que no requerían almacenamiento de datos. Sin embargo, en algunas aplicaciones, el nanoprocesador usaba RAM como dispositivo de E / S. Se envió una dirección a uno de los puertos de E / S y se leyó un byte de datos del otro. Fotomáscaras combinadas con nanoprocesador (se puede hacer clic) De la imagen de la fotomáscara anterior, podemos concluir que el nanoprocesador es simple. Las líneas azules son conductores de metal en la parte superior del chip, las verdes son silicio con impurezas. Cuadrados negros alrededor del perímetro: 40 almohadillas para comunicación con contactos externos del IC. Las pequeñas áreas negras del interior son transistores. Si miras de cerca, puedes contar 4.639 de ellos.

Si tenemos en cuenta que el decodificador de instrucciones consta de pares de transistores pequeños, lo que se hace para la conveniencia de la disposición de los componentes, y contamos estos pares como uno, obtenemos 3829 transistores. De estos, 1061 son dominadas y 2668 activos. En comparación, el 6502 tenía 4.237 transistores, 3.218 de los cuales estaban activos. El 8008 tenía 3.500 transistores, mientras que el Motorola 6800 tenía 4.100.

El siguiente diagrama de bloques muestra la estructura interna del nanoprocesador. En el medio hay 16 registros de explotación. El comparador le permite comparar dos valores para proporcionar una ramificación condicional. La unidad lógica de control se ocupa de las operaciones de incremento, decremento, desplazamiento y bit del acumulador. No tiene las operaciones aritméticas y lógicas de la ALU estándar. El contador de programa (derecha) recupera una instrucción del registro de instrucciones (izquierda); Las interrupciones y las llamadas a subrutinas tienen sus propias pilas de un elemento para almacenar direcciones de retorno.

Diagrama de flujo de trabajo de las instrucciones para Nanoprocesador

Permítanme enfatizar que, a pesar de su simplicidad y falta de operaciones aritméticas, Nanoprocessor no es una especie de procesador de "juguete" que cambia las líneas de control. Es un procesador rápido y potente que se utiliza para realizar operaciones complejas. Por ejemplo, el módulo de reloj en tiempo real HP 98035 usó Nanoprocesador para procesar dos docenas de cadenas de control ASCII diferentes, así como para contar la cantidad de días en un mes.

Un proyecto interesante para divertirse puede ser la creación de una versión FPGA de Nanoprocessor, ya que Nanoprocessor es quizás la versión más simple de un procesador comercial real. Las instrucciones describen todos los comandos y dan ejemplos de código que puede ejecutar.

Registros

La foto del cristal de abajo muestra que una parte significativa del nanoprocesador está ocupada por sus 16 registros. Se comunican con el resto de componentes a través del bus de datos. Las cadenas en la parte superior seleccionan un registro en particular. Registre R0, a la derecha, junto al comparador.

Una parte significativa del nanoprocesador está ocupada por sus registros 16.

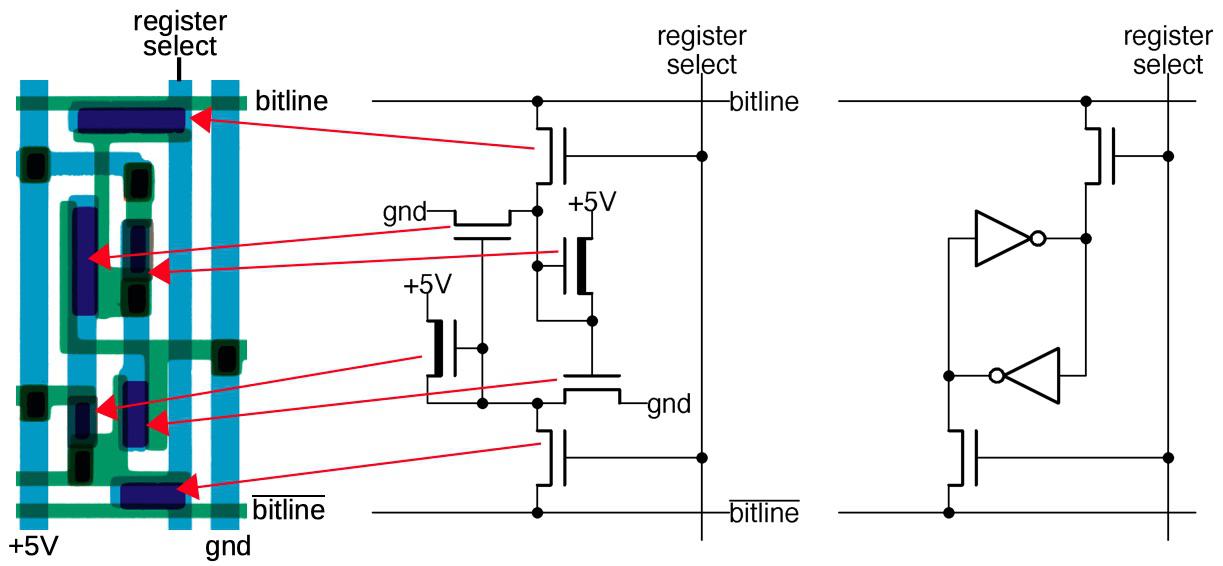

El bloque de construcción de un registro son dos inversores en el circuito de retroalimentación, que almacenan un bit como se muestra a continuación. Si el conductor superior es 0, el inversor derecho emitirá 1 al conductor inferior, luego el inversor izquierdo emitirá un 0 al conductor superior, completando el ciclo. El circuito permanece estable "recordando" 0. De la misma manera, si el conductor superior es 1, se invierte a 0 en la parte inferior y de nuevo a 1 en la parte superior. La red puede almacenar 0 o 1 de esta manera, formando una ubicación de memoria de 1 bit.

Dos inversores en un circuito de almacenamiento de bits estable

El siguiente diagrama muestra cómo se implementa este almacenamiento de dos inversores en un chip. La ubicación física de los componentes se muestra a la izquierda, basada en una fotomáscara. El diseño está optimizado para que la celda ocupe el menor espacio posible. Líneas azules - capa de metal, verde - silicona. En el medio, se muestra un diagrama del circuito correspondiente con transistores. Cada inversor consta de un par de transistores como se muestra a la derecha. Los transistores en la parte superior e inferior son "pasantes", proporcionan acceso a la celda de almacenamiento.

Almacenamiento de un bit en nanoprocesador. Cada bit se implementa en 6 transistores (celda 6T SRAM).

Un conjunto de registros consta de una matriz de dichas celdas de bits. El bus de selección de registro selecciona un registro (una columna) para lectura o escritura. Los transistores de paso superior e inferior luego conectan los inversores a sus respectivas líneas de bits horizontales. Para la lectura, la línea de bits superior proporciona el valor almacenado en la celda; hay ocho líneas de bits para los ocho bits almacenados en el registro. Para escribir, el valor se transfiere a la línea de bits superior y el valor invertido se transfiere a la inferior. Estos valores reemplazan las señales de los inversores, haciendo que tomen el valor deseado y almacenen este bit. Por tanto, una cuadrícula de líneas de bits horizontales y líneas de selección verticales permite leer o escribir un valor en un registro particular.

Comandos de decodificación

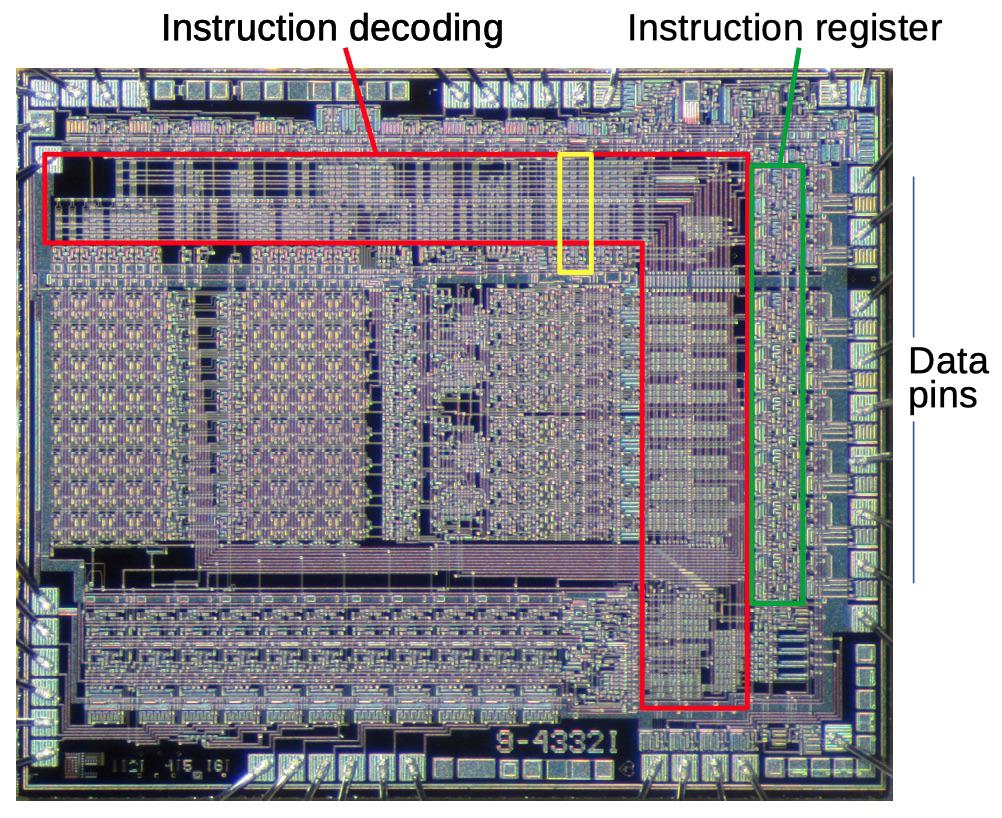

Los circuitos de decodificación se dedican a tomar el código binario de la instrucción (por ejemplo, 01101010) y determinar cuál es la instrucción (en este caso, "acumulador de carga del registro 10"). En comparación con muchos procesadores, las instrucciones del nanoprocesador son bastante simples: tiene relativamente pocas (48) y el código de instrucción es siempre de un byte. El siguiente diagrama muestra que la lógica de decodificación de instrucciones (rojo) ocupa una parte significativa del chip. El registro de instrucción (verde) es un conjunto de ocho pestillos que contienen la instrucción actual. El registro de comando se encuentra junto a los pines de datos a los que proviene el comando desde la ROM. En esta sección, desglosaremos la cadena de decodificación que se muestra en amarillo.

La decodificación se realiza mediante puertas NOR. Cada puerta NOR reconoce un comando o grupo de comandos específico. La puerta NOR acepta bits de comando o su complemento como entrada. Cuando todos los bits entrantes son cero, la puerta NOR informa una coincidencia. Esto le permite buscar partidos tanto en todo el equipo como un todo y en parte del equipo. Por ejemplo, el comando "cargar acumulador del registro R" tiene un formato binario 0110rrrr, en el que los últimos cuatro bits indican el registro requerido. La puerta NOR (bit7 + bit6 '+ bit5' + bit4) 'coincidirá con este comando.

Un decodificador de instrucciones estructurado de esta manera es bueno porque puede ensamblarse a partir de circuitos compactos y repetitivos. A menudo se llama PLM (matriz lógica programable). La idea es que las señales entrantes a la matriz se alimenten horizontalmente y las salientes se alimenten verticalmente. En cada intersección puede haber un transistor, y luego la señal de entrada es parte de la puerta; si no hay transistor, esta entrada se ignora. El resultado son válvulas NOR dispuestas de forma compacta. En los primeros microprocesadores, el decodificador a menudo se hacía a partir de una matriz de puertas NOR; por ejemplo, este era el caso del 6502.

El siguiente diagrama muestra tres decodificadores agrandados en el lado derecho, que están encerrados en un círculo amarillo en el diagrama de arriba. Este diagrama corresponde al decodificador más a la izquierda. Preste atención a la correspondencia de los transistores en el diagrama con los puntos rosados de los transistores en el diseño. La idea es que si alguna señal de entrada activa el transistor, entonces el transistor lleva la señal de salida a tierra. De lo contrario, la salida se eleva mediante una resistencia. Los inversores en la parte inferior amplifican la señal para que haya suficiente corriente para alimentar las ocho partes de la batería. Curiosamente, este diseño usa pares de transistores con tierra y salida conectadas; no veo ninguna ventaja sobre el uso de un solo transistor. En cualquier caso, observe cómo el PLM proporciona una disposición densa de decodificadores.

Tenga en cuenta que el inversor en el decodificador de instrucciones se eleva a 12 V, no a 5 V. Esto se debe a que el nanoprocesador utiliza transistores de puerta de metal en lugar de los transistores de puerta de silicio más avanzados que se encuentran en otros microprocesadores de la época. La desventaja de un transistor con una puerta de metal es un voltaje de umbral aumentado, por lo que el voltaje de salida del transistor es mucho más bajo que el voltaje en la puerta. La salida de un inversor convencional es demasiado pequeña para alimentar la puerta del transistor de paso, ya que su voltaje de salida caerá nuevamente. La solución es utilizar una fuente de alimentación de 12 V para los inversores del decodificador que controla los transistores de bypass de la batería, entonces las señales tendrán suficiente voltaje para activar los transistores de paso. En otras palabras, el nanoprocesador necesita más de 12 V adicionales,porque utiliza transistores de puerta de metal en lugar de los transistores de puerta de silicio más avanzados.

Uno de los circuitos decodificadores de nanoprocesador. El diagrama de la izquierda corresponde al decodificador más a la izquierda de los tres que se muestran a la derecha.

Este circuito genera una señal de incremento / decremento que se alimenta al circuito acumulador. El renglón detecta una coincidencia cuando el nivel de señal del generador de reloj, la solicitud, el sexto bit de comando y el segundo bit de comando es bajo; se encuentra una coincidencia como x0xxx0xx durante la fase de ejecución. Estos comandos incluyen "Incremento binario" (00000000), "Incremento BCD" (00000010), "Decremento binario" (00000001) y "Decremento BCD" (00000011).

La cadena que se muestra en el diagrama busca coincidencias con comandos de la forma x0xxx0xx, por lo que la coincidencia se encuentra con muchos más comandos que solo incrementar y disminuir. ¿Por qué no busca una pareja completa? La razón es que si el acumulador no está en uso, la activación de la señal de incremento / decremento es irrelevante. Al expandir la lista de opciones coincidentes, los desarrolladores podrían deshacerse de algunos de los transistores en el circuito. Es importante que la cadena anule otras instrucciones relacionadas con la batería como "Limpiar acumulador" (00000100) o "Cargar acumulador del registro" (0110rrrr).

Comparador

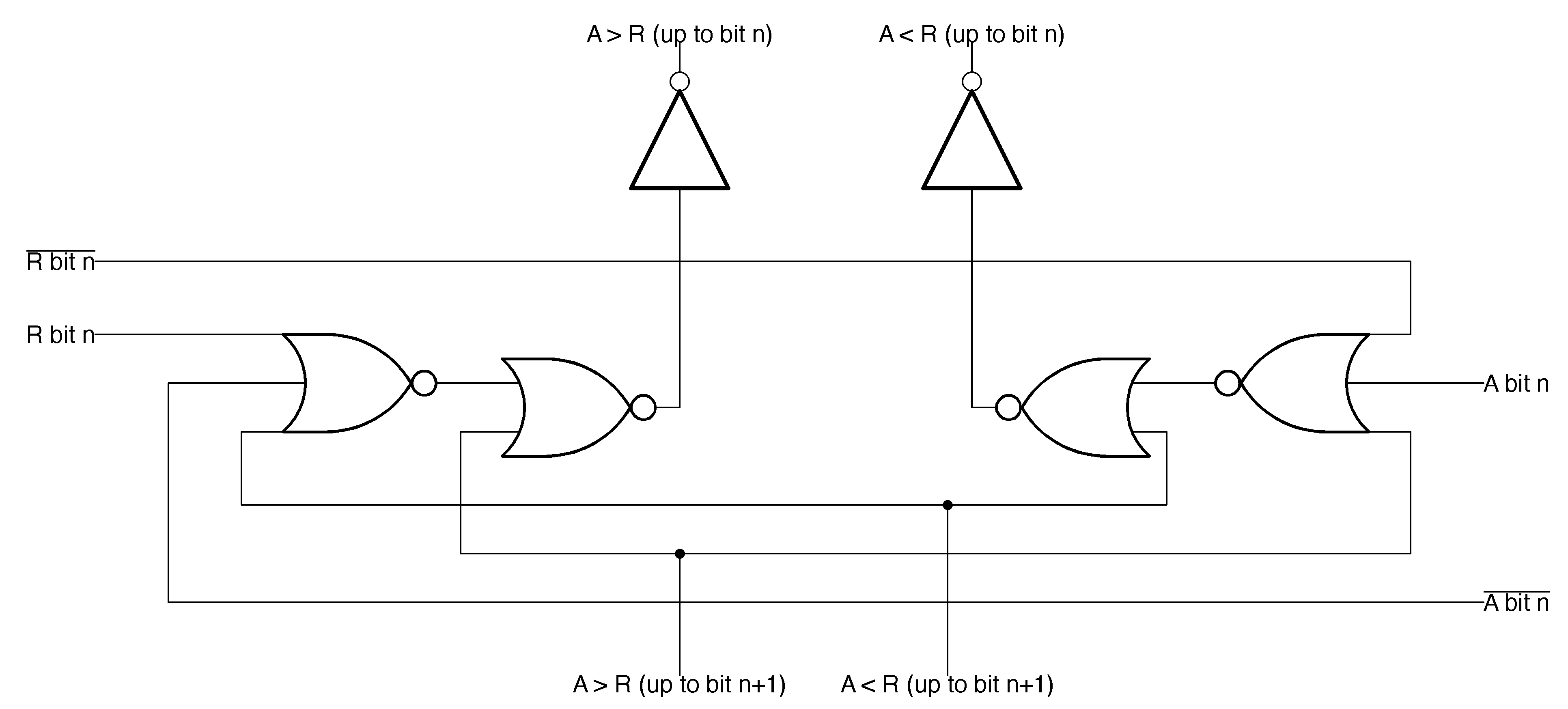

Un circuito nanoprocesador importante es un comparador que compara el valor almacenado en el acumulador con el valor del registro R0. El comparador usa un circuito único pero complicado para compararlos. Esencialmente, el algoritmo compara dos números que comienzan con los bits más significativos. Si los bits son iguales, continúe con los inferiores. La primera diferencia de bit determina qué valor es mayor (por ejemplo, en el caso de 10101010 y 10100111, esto determina el cuarto bit desde la derecha).

El algoritmo se implementa en ocho pasos, uno a la vez, comenzando con el bit más significativo en la parte inferior. Cada paso consta de dos partes simétricas: una determina si la desigualdad A> R0 se cumple y su parte adicional verifica la desigualdad A <R0. Si los números siguen siendo iguales, pero se encuentra una diferencia en esta etapa, la etapa genera una señal "más" o "menos". De lo contrario, pasa la decisión a un nivel inferior. La decisión final la toma el peldaño más alto. Tenga en cuenta que la comparación de igualdad en el comparador se realiza "gratis"; si no hay señales "más" o "menos" en la salida, los valores son iguales.

Una de las etapas de un comparador de 8 bits

El diagrama siguiente muestra el diseño físico de las dos etapas del comparador. Un truco en el diseño del comparador es que se encuentra entre el registro 0 a la izquierda y el acumulador a la derecha, lo que minimiza la longitud de los cables. El comparador accede al registro 0 directamente, sin pasar por las rutas habituales de selección de registro y bus de datos.

Dos etapas del comparador, tal como se especifica en la fotomáscara

Los comandos de ramificación condicional del nanoprocesador pueden inspeccionar la salida del comparador. Los circuitos de bifurcación condicionales son bastante simples: unos pocos bits de la instrucción de bifurcación seleccionan una verificación particular a través del multiplexor. Luego, el séptimo bit del comando decide si seleccionar "esta rama si es verdadera" o "esta rama si es falsa". A diferencia de la mayoría de los procesadores, Nanoprocessor no permite la ramificación a ninguna dirección. Simplemente omite dos bytes de comando si se cumple la condición (y normalmente estos dos bytes contienen el comando para ir al destino deseado, pero a veces hay otros comandos). El esquema de omisión es simple: se vuelve a llamar al contador del programa, mientras se aumenta el valor no en 1, sino en 2, omitiendo dos comandos. Resulta que Nanoprocessor implementa una amplia gama de verificaciones condicionales en un número relativamente pequeño de redes.

El nanoprocesador tiene un gran conjunto de condiciones de ramificación, sorprendentemente grande para un procesador tan simple. Puede comprobar las siguientes condiciones: A> R0, A> = R0, A <R0, A <= R0, A == R0 o A! = R0. Además, la bifurcación condicional puede depender de si el valor en el acumulador es cero o no, si un bit específico del valor almacenado en el acumulador es igual a cero, si el indicador de desbordamiento está establecido o si un bit específico del registro de E / S está establecido.

Dispositivo lógico de control y batería

El acumulador es un registro especial de 8 bits que almacena el byte que se está procesando actualmente. Las operaciones con la batería se llevan a cabo mediante un dispositivo lógico de control (ULU), que se denomina "corazón del nanoprocesador" en las instrucciones del procesador. ULU es el equivalente de una unidad aritmética lógica (ALU) en la mayoría de los procesadores, solo que no realiza operaciones aritméticas o lógicas. Al mismo tiempo, ULU no es tan inútil como parece a primera vista. Puede incrementar o disminuir el valor en el acumulador, ya sea en binario o en decimal codificado en binario (BCD). El BCD almacena dos lugares decimales en un byte. Este es un modo muy útil para E / S o pantallas. La ULU también puede encontrar el complemento binario del acumulador o restablecerlo, así como establecer y borrar un cierto bit. Finalmente,admite operaciones de desplazamiento a izquierda y derecha.

Circuitos relacionados con la batería

El diagrama anterior muestra los circuitos de la batería y del ULD. En la primera sección, se ubican varias redes, definiendo un valor cero, soportando BCD y proporcionando arrastre - generación rápida de un arrastre a partir de los 4 bits menos significativos. La segunda sección contiene la batería principal y los circuitos ULU. La tercera sección distribuye señales de control de la lógica de decodificación anterior a las ocho partes del acumulador. La última sección contiene la lógica de decodificación de instrucciones que decodifica las operaciones de bit y envía la señal a la parte deseada del acumulador.

El cuerpo principal del acumulador / ULU consta de 8 partes, una por bit, con el bit menos significativo en la parte superior. Veremos cuatro circuitos de cada parte: un generador de acarreo para operaciones de incremento / decremento, un generador de bits para operaciones de incremento / decremento, un multiplexor para seleccionar un nuevo valor de acumulador y un pestillo donde se almacena el valor del acumulador.

Cada parte del dispositivo de incremento / decremento (abajo) se implementa usando un medio sumador. La dirección de la cadena de incremento / decremento determina el código de operación: 0 en el bit de orden inferior del código de operación dice incremento y 1 para decremento. La cadena de acarreo de la izquierda genera la señal de acarreo. Para un incremento, cree una salida de acarreo si se recibe una entrada de acarreo y el bit actual es 1 (ya que entonces se incrementará a 10 binario). Para el decremento, la línea de acarreo indica un préstamo , por lo que se genera una salida de acarreo cuando hay una entrada de acarreo (es decir, pedir prestado) y el bit actual es 0.

Una parte de la cadena de incremento / decremento

El renglón de la derecha actualiza el bit actual con un incremento o decremento. El bit actual se alterna cuando está presente una entrada de acarreo, esencialmente una implementación XOR a través de tres puertas NOR. Una de las dificultades es el ajuste de BCD. Para la operación de incremento de BCD, el acarreo ocurre cuando se incrementa el dígito 9, y para la operación de decremento de BCD, el dígito 0 disminuye a 9 en lugar del binario 1111.

El multiplexor gestiona las distintas operaciones de la batería. Dependiendo de la operación, se activa un transistor de un paso, seleccionando el valor deseado. Por ejemplo, para una operación de incremento / decremento, el transistor superior selecciona la salida del circuito de incremento / decremento descrito anteriormente. El transistor activa el decodificador de instrucciones descrito anteriormente, que ha encontrado la instrucción de incremento / decremento correspondiente. Del mismo modo, un comando de cambio a la derecha activa un transistor de cambio a la derecha aplicando n + 1 bits de batería a cada una de las partes del acumulador para cambiar el valor.

Circuito para un pestillo que almacena un bit de la batería y un multiplexor que selecciona la entrada para la batería

El pestillo almacena un bit para el acumulador. Cuando se activa el transistor de retención de batería, las dos puertas NOR forman un bucle de retención. Si, en cambio, se activa el transistor de carga de la batería, la batería carga el valor deseado del multiplexor. Las líneas para borrar el bit n y establecer el bit n permiten comandos para cambiar bits individuales del acumulador; el multiplexor actualiza todos los bits del acumulador a la vez.

Direccionamiento de programas y contadores

Otro gran bloque de cadenas es el contador de programa de 11 bits ubicado en la esquina inferior izquierda del nanoprocesador. También en este bloque hay un pestillo que almacena la dirección de retorno de la subrutina y otro pestillo que almacena el contador del programa después de la interrupción. Piense en ellos como una pila de un elemento de largo. El contador de software tiene un dispositivo de incremento que es responsable de pasar al siguiente comando. También sabe cómo incrementar en dos a la vez, lo que permite que las instrucciones de bifurcación condicional salten dos instrucciones (un dispositivo de incremento de este tipo se implementa simplemente aumentando el primer bit en lugar del 0). Para acelerar el funcionamiento del dispositivo de incremento, tiene una función de transferencia; si los seis bits menos significativos son 1, incrementará el sexto bit a la vez, sin esperar a que el acarreo pase por todos los bits menos significativos.

Control y frecuencia de reloj

La última parte del nanoprocesador es el circuito de control. En comparación con otros microprocesadores, el esquema de control del nanoprocesador parece casi trivial: el procesador pasa del reloj de solicitud al reloj de ejecución y viceversa (con interrupciones periódicas). El circuito de control es solo un par de flip-flops y puertas, por lo que no hay mucho que decir al respecto.

Conclusión

El siguiente diagrama muestra los principales bloques funcionales de Nanoprocessor. El nanoprocesador se las arregló para ajustarlos muy bien, mucho mejor de lo que esperaría de la anticuada tecnología de obturadores metálicos. La ingeniería inversa muestra que estos bloques funcionales se implementan con circuitos simples pero cuidadosamente diseñados.

El nanoprocesador utiliza transistores de puerta de metal, mientras que otros microprocesadores han comenzado a cambiar a transistores de puerta de silicio durante varios años. La diferencia puede parecer incomprensible, pero tiene un efecto significativo en la ubicación de los componentes: en la fabricación de un transistor con puertas de silicio, se agrega una capa de polisilicio con conductores. Esto hace que sea mucho más fácil colocar los componentes, ya que tiene dos capas de conductores a su disposición que pueden atravesar la capa adyacente. Si solo tiene una capa de metal, es mucho más difícil colocar los componentes porque los conductores se interponen en el camino. En otros chips he estudiado que usaban tecnología de transistores de puerta metálica,el diseño de los componentes era repugnante: un montón de cables enredados que llevaban señales a cada transistor mantenían baja la densidad de los transistores. Por otro lado, los bloques de funciones del nanoprocesador están diseñados con mucho cuidado y todas las señales se llevan bien. Hay un poco de espacio adicional, por ejemplo, para el bus de datos, pero en general estoy impresionado con la densidad del diseño del nanoprocesador.

Componentes funcionales del nanoprocesador basados en mi

nanoprocesador de ingeniería inversa: el procesador es inusual. A primera vista, incluso me pareció un "procesador falso", debido a la falta de operaciones aritméticas básicas. Sin embargo, después de estudiarlo con más detalle, todavía estaba impresionado. Su diseño simple le permite funcionar más rápido que otros procesadores de la época. El conjunto de comandos puede hacer más de lo que parece. Hewlett-Packard usó Nanoprocessor en muchos de sus productos en las décadas de 1970 y 1980, en funciones más complejas de lo que cabría esperar, por ejemplo, analizar cadenas y realizar cálculos. Después de que se hayan publicado sus máscaras, podemos aprender todos los secretos de las cadenas gracias a las cuales funcionó Nanoprocessor.

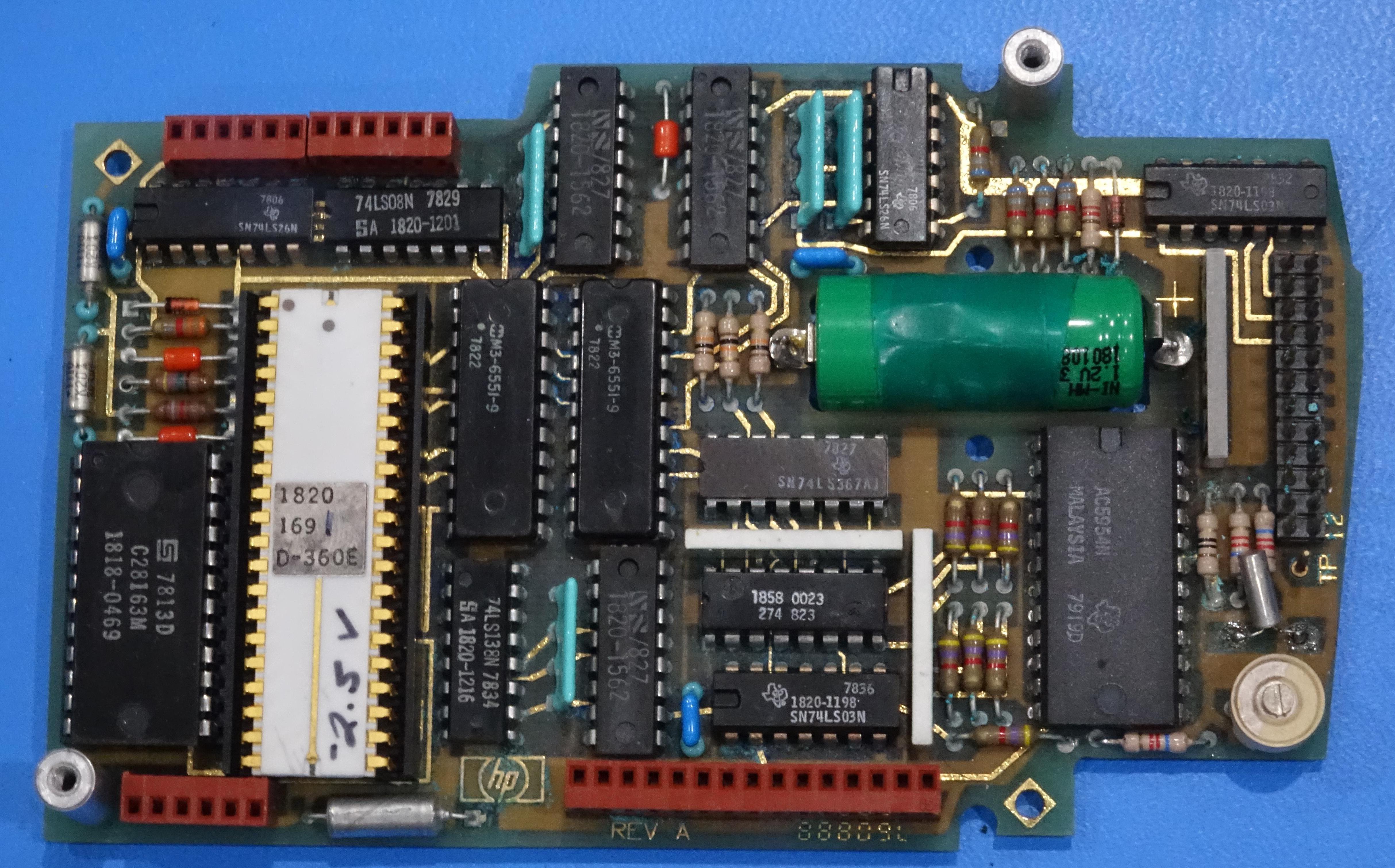

Nanoprocesador (chip blanco) como parte del módulo de sincronización de precisión de Hewlett-Packard. Tenga en cuenta el voltaje escrito a mano; cada chip requería su propio voltaje de polarización.