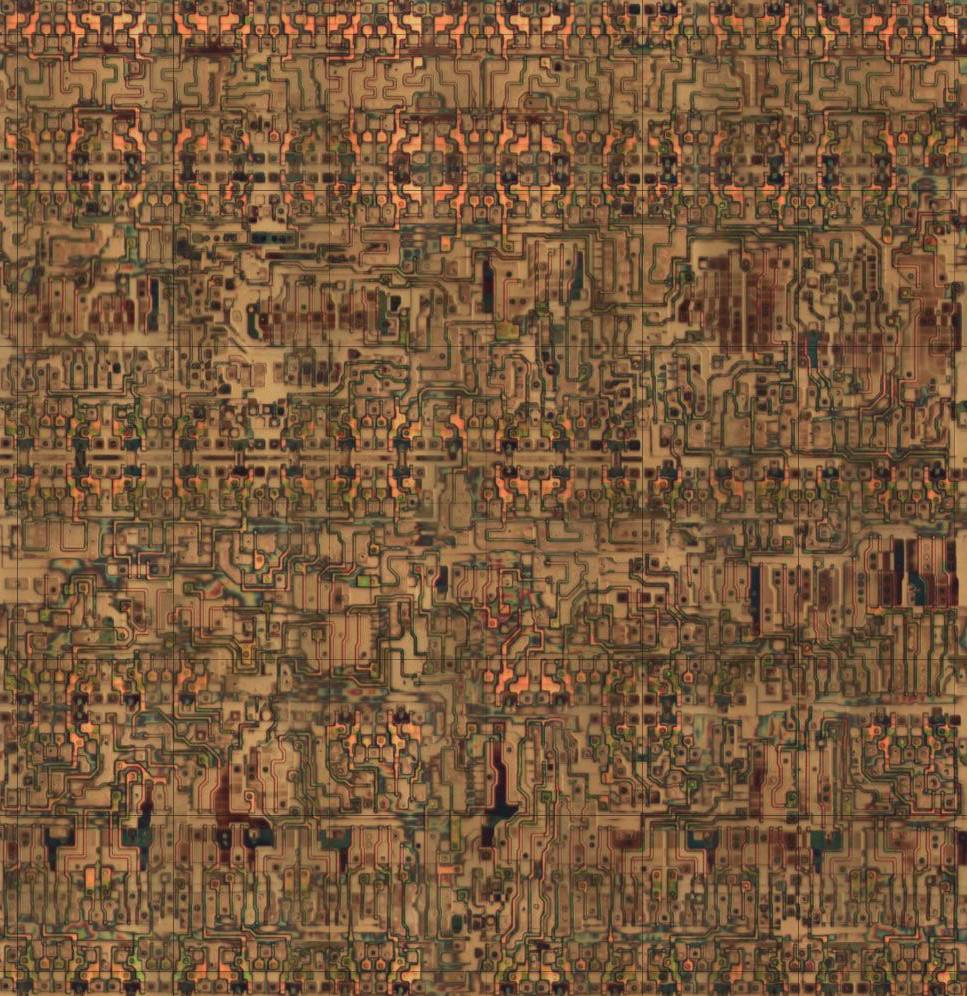

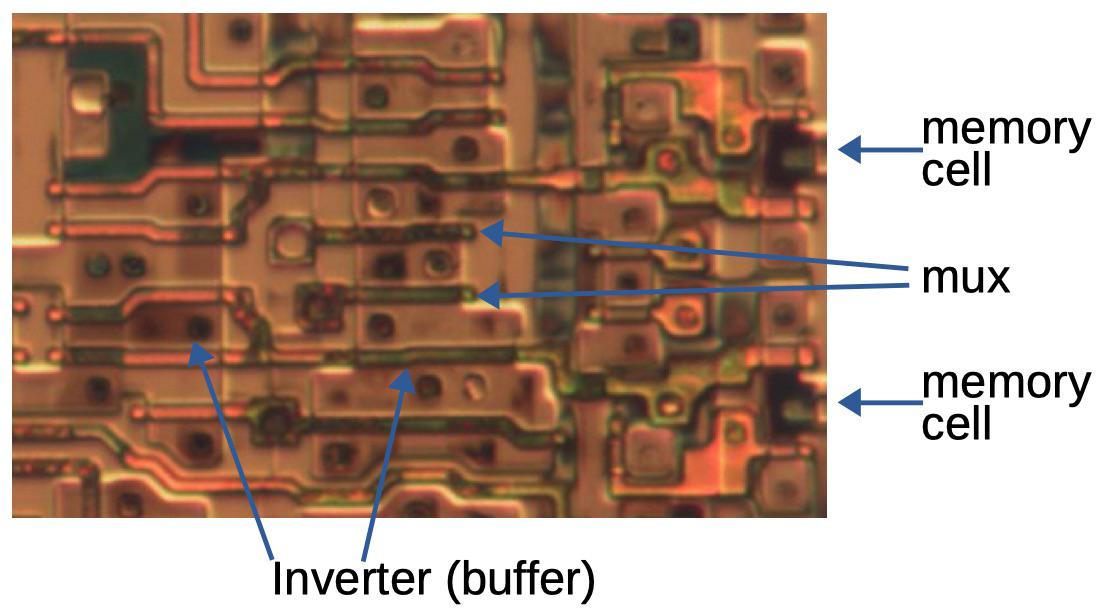

La foto muestra uno de los 64 bloques del chip XC2064. Las capas de metalización se eliminan, podemos ver transistores de silicio y polisilicio debajo de la metalización. Puedes ver una foto a mayor escala aquí: siliconpr0n .

La FPGA fue inventada por Ross Freeman, cofundador de Xilinx en 1984, la primera FPGA fue la XC2064. Era mucho más simple que los FPGA modernos, contenía solo 64 bloques lógicos, en comparación con los miles y millones de los FPGA modernos, y su creación condujo al surgimiento de una industria valorada en miles de millones de dólares. El XC2064 es tan importante que entró en el Salón de la Fama de Chips. He realizado ingeniería inversa del XC2064 y en este post explico su estructura interna en términos generales y cómo se programa con un bitstream.

Xilinx

Xilinx -. , , Xilinx , . Xilinx Seiko Epson Semiconductor Division ( Seiko Epson).

XC2064

: ( ) . — (Programmable Logic Devices, PLD), , , 1967 . , , , . , PROM, , , EPROM, . , , Programmable Logic Array, Programmable Array Logic (1978), Generic Array Logic Uncommitted Logic Array. , , « », . , , , , , . , . "Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology." "A Brief History of FPGAs".

Xilinx XC2064 es el primer chip FPGA. Tomado de aquí: siliconpr0n .

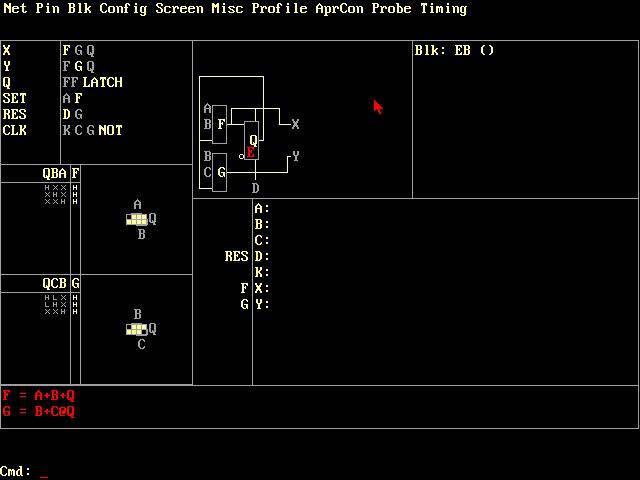

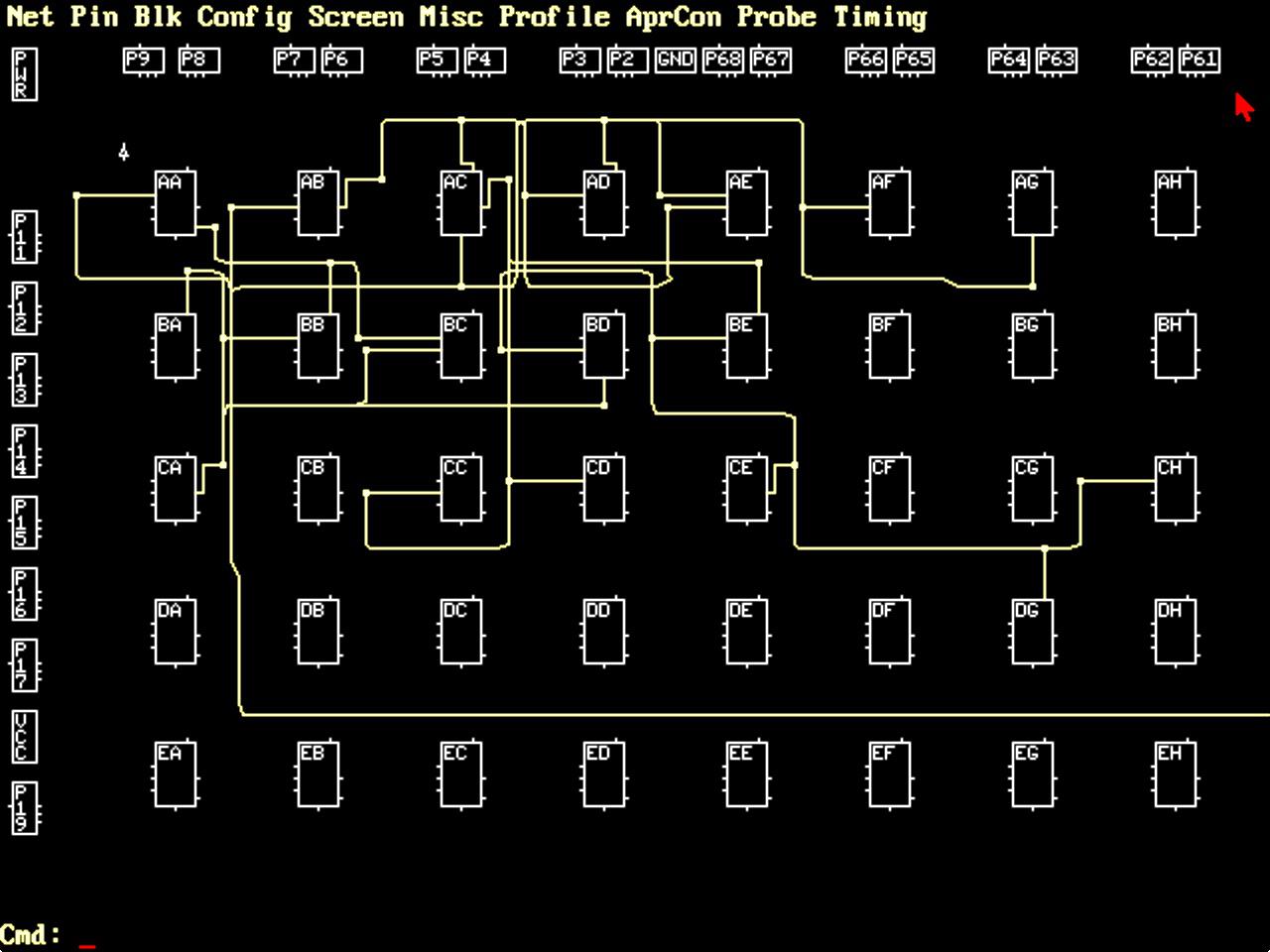

Los FPGA están actualmente programados en lenguajes de descripción de hardware como Verilog o VHDL, pero en ese momento, Xilinx proporcionó su propio software de desarrollo, una aplicación MS-DOS llamada XACT, por los considerables $ 12,000. XACT trabajó a un nivel más bajo que las herramientas modernas: el usuario definió la función de cada bloque lógico, como se muestra en la captura de pantalla a continuación, y las conexiones entre los bloques lógicos.

XACT encaminó las conexiones y generó un archivo de configuración (bitstream) que se cargó en la FPGA.

Captura de pantalla de XACT. Las dos tablas F y G implementan las ecuaciones que se muestran en la parte inferior de la pantalla, con el mapa de Karnaugh que se muestra arriba.

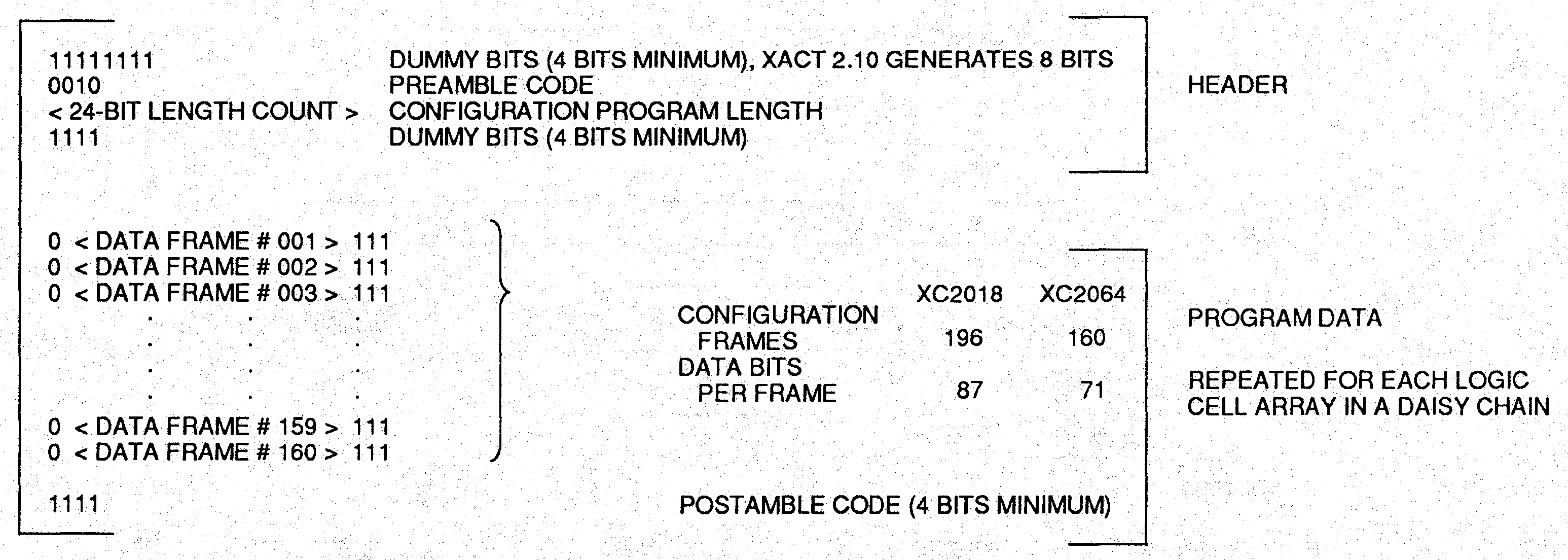

La FPGA se configuró utilizando un flujo de bits, una secuencia de bits en un formato propietario. Si observa el flujo de bits XC2064 (abajo), verá una misteriosa mezcla de patrones que se repiten de manera irregular y están dispersos por todo el flujo de bits. Sin embargo, el estudio de los circuitos físicos de la FPGA revela la estructura de datos del flujo de bits y se puede estudiar.

Parte del flujo de bits generado por XACT.

¿Cómo funciona FPGA?

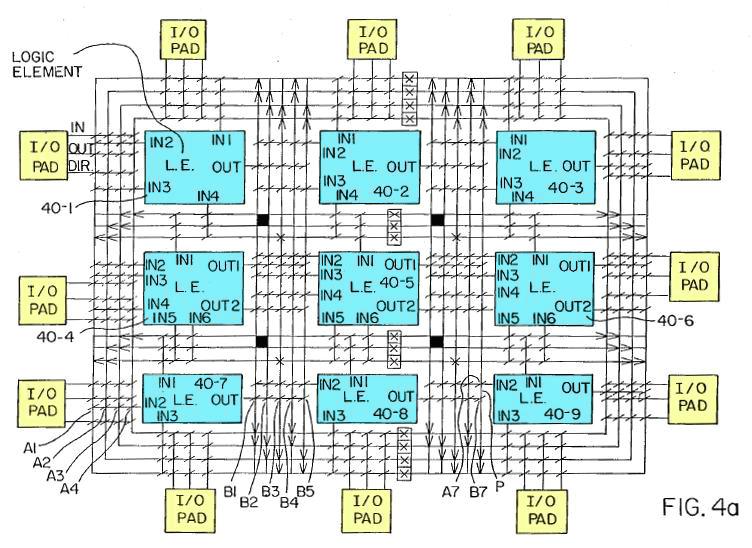

La siguiente figura, tomada de la patente FPGA original, muestra la estructura básica de una FPGA. Este FPGA simplificado tiene un total de 9 bloques lógicos (marcados en azul) y 12 puertos de E / S. Una red de interconexión conecta los componentes. Al configurar interruptores (líneas diagonales) en las conexiones, los bloques lógicos se pueden conectar entre sí y a los puertos de E / S. Cada elemento lógico se puede programar para la función lógica requerida. Como resultado, dicho chip programable puede implementar cualquier dispositivo que encaje en el espacio disponible.

Patente FPGA , bloques lógicos (LE) interconectados.

Bloque lógico configurable (CLB)

Aunque la imagen de arriba muestra 9 CLB, el XC2064 tiene 64 CLB. La siguiente figura muestra la estructura del CLB. CLB tiene 4 entradas (A, B, C, D) y dos salidas (X e Y). En el medio está la lógica combinacional, que se puede programar para cualquier función lógica deseada. El CLB también contiene un disparador, cuya presencia le permite implementar contadores, registros de desplazamiento, máquinas de estado y otros circuitos con estado. Los trapecios indican multiplexores que pueden programarse para pasar una señal desde cualquiera de las entradas. Los multiplexores le permiten configurar el CLB para una tarea específica mediante la selección de señales específicas para controlar el disparador y las salidas.

Bloque lógico configurable en XC2064, tomado de aquí: hoja de datos .

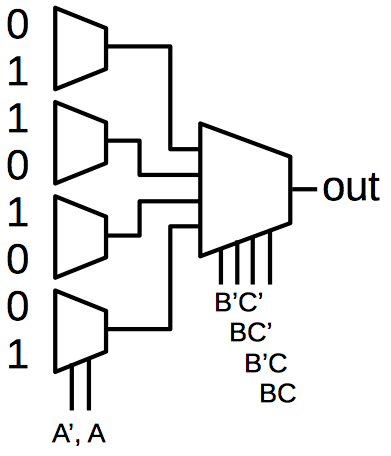

Quizás se esté preguntando cómo la lógica combinacional implementa funciones lógicas arbitrarias. ¿Se puede elegir entre un conjunto de AND, OR, XOR, etc.? No, hay un truco inteligente llamado tabla de búsqueda (LUT), que en realidad es la tabla de verdad para la función. Por ejemplo, una función de tres variables se define mediante una tabla de 8 filas. La LUT contiene 8 bits de memoria. Podemos implementar cualquier función lógica de 3 entradas manteniendo esos tres bits.

Ver tablas

XC2064 — , . CLB . XC2064 , 4 . , .

XC2064 . .

XC2064 . .

Conexiones

El siguiente aspecto clave de los FPGA son las conexiones, que se pueden programar para cambiar el CLB de varias formas. Las conexiones son complejas, pero la descripción aproximada es que hay segmentos de conexiones verticales y horizontales entre todos los CLB. Puede conectar CLB con líneas horizontales y verticales y crear conexiones arbitrarias. Un tipo de conexión más complejo es la "matriz de conmutación". Cada matriz tiene 8 pines que se pueden conectar entre sí (casi) de cualquier manera.

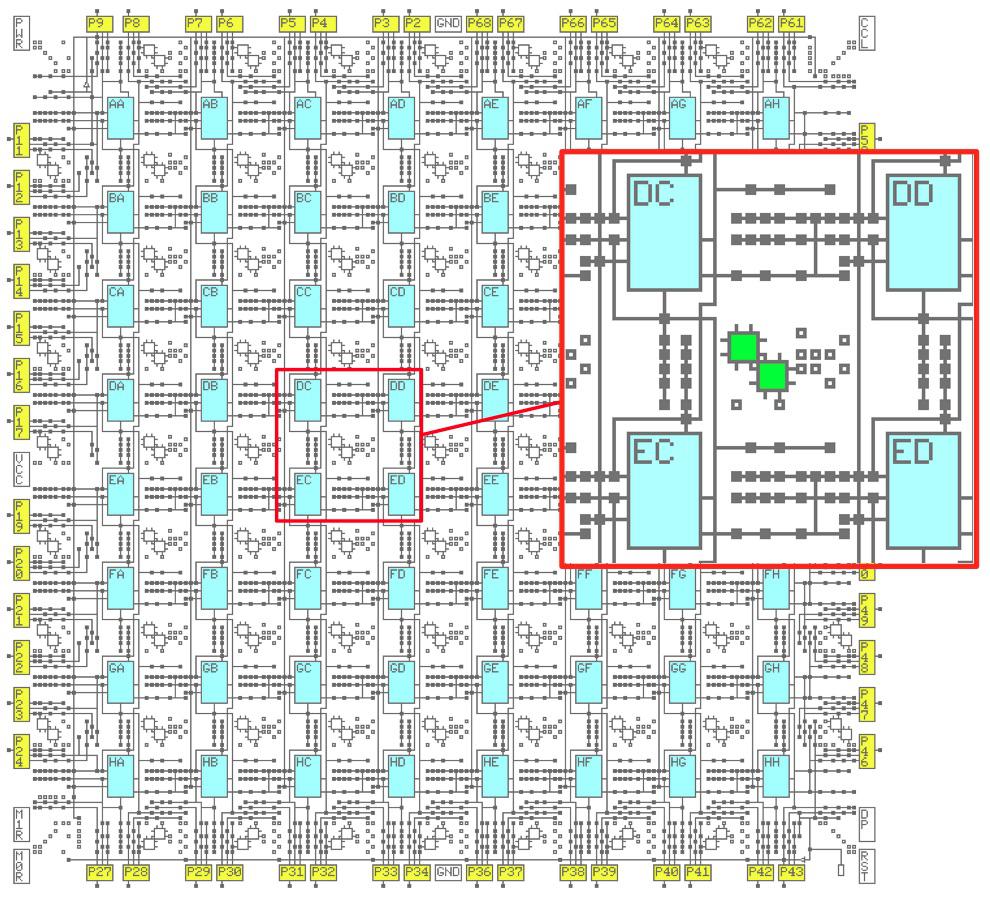

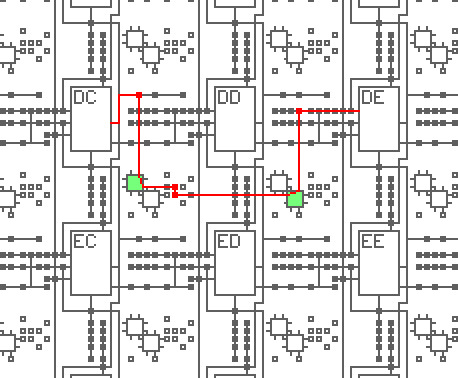

La siguiente figura muestra la estructura de los enlaces XC2064 que proporcionan conexiones entre bloques lógicos (azul) y líneas de E / S (amarillo). El recuadro muestra los detalles del mecanismo de acoplamiento. Los rectángulos verdes son matrices de interruptores de 8 pines y los cuadrados pequeños son puntos de conexión programables.

El FPGA XC2064 tiene una matriz CLB de 8x8. Cada CLB tiene un nombre de AA a HH.

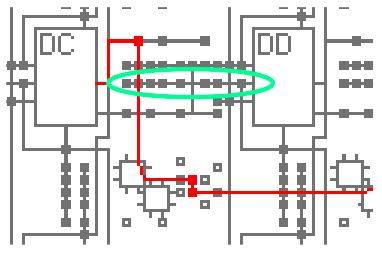

La conexión puede cambiar, por ejemplo, la salida de un bloque de CC a una entrada de un bloque DE, como se muestra a continuación. La línea roja muestra la ruta de la señal y los pequeños cuadrados rojos muestran los puntos de conexión activados. Al salir del bloque de CC, la señal se enruta al primer punto de conexión en un interruptor de 8 pines (verde), que la encamina a través de dos puntos de conexión y otro interruptor de 8 vías (no se muestran las líneas verticales y horizontales no utilizadas). Tenga en cuenta que la conexión es bastante compleja, incluso una ruta tan corta utiliza cuatro puntos de conexión y dos interruptores.

Ejemplo de enrutamiento de señales desde la salida de un bloque de CC a un bloque DE.

La siguiente captura de pantalla muestra cómo se realiza el seguimiento en XACT. Las líneas amarillas muestran conexiones entre bloques lógicos. A medida que aumenta el número de señales, resulta difícil establecer conexiones sin conflictos entre las rutas. XACT rastrea automáticamente, pero el rastreo también se puede editar manualmente.

Captura de pantalla del programa XACT. Es un programa de MS-DOS y está controlado por teclado y mouse.

Implementación

A continuación, veremos los circuitos internos del XC2064 mediante ingeniería inversa a partir de una foto del cristal. Te advierto que esto requiere cierta familiaridad con XC2064.

Foto de cristal

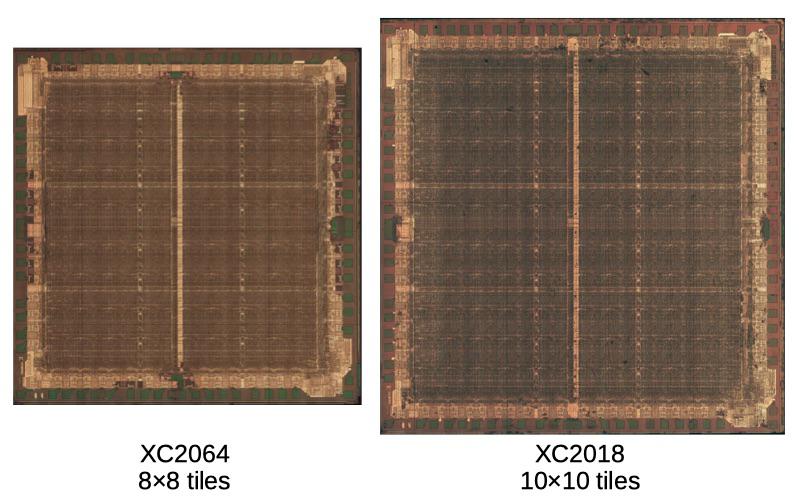

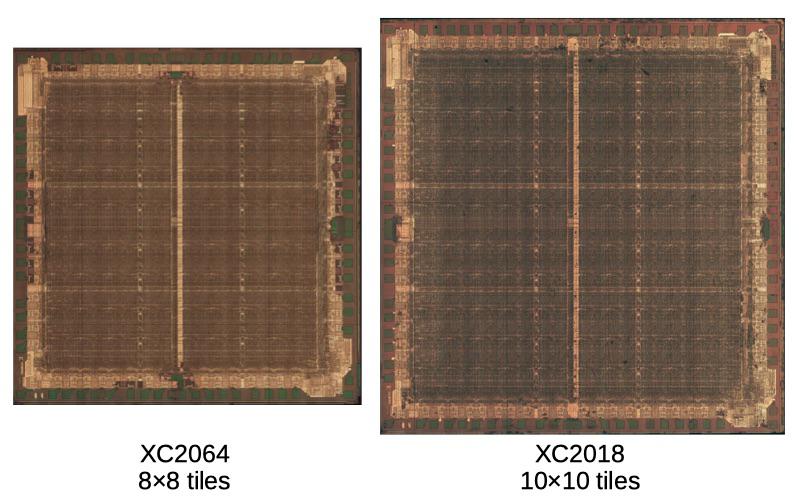

XC2064 XC20186, XC2064 XC2018 siliconpr0n. , . John McMaster , , . , .

XC2064 , John McMaster.

XC2064 , John McMaster.

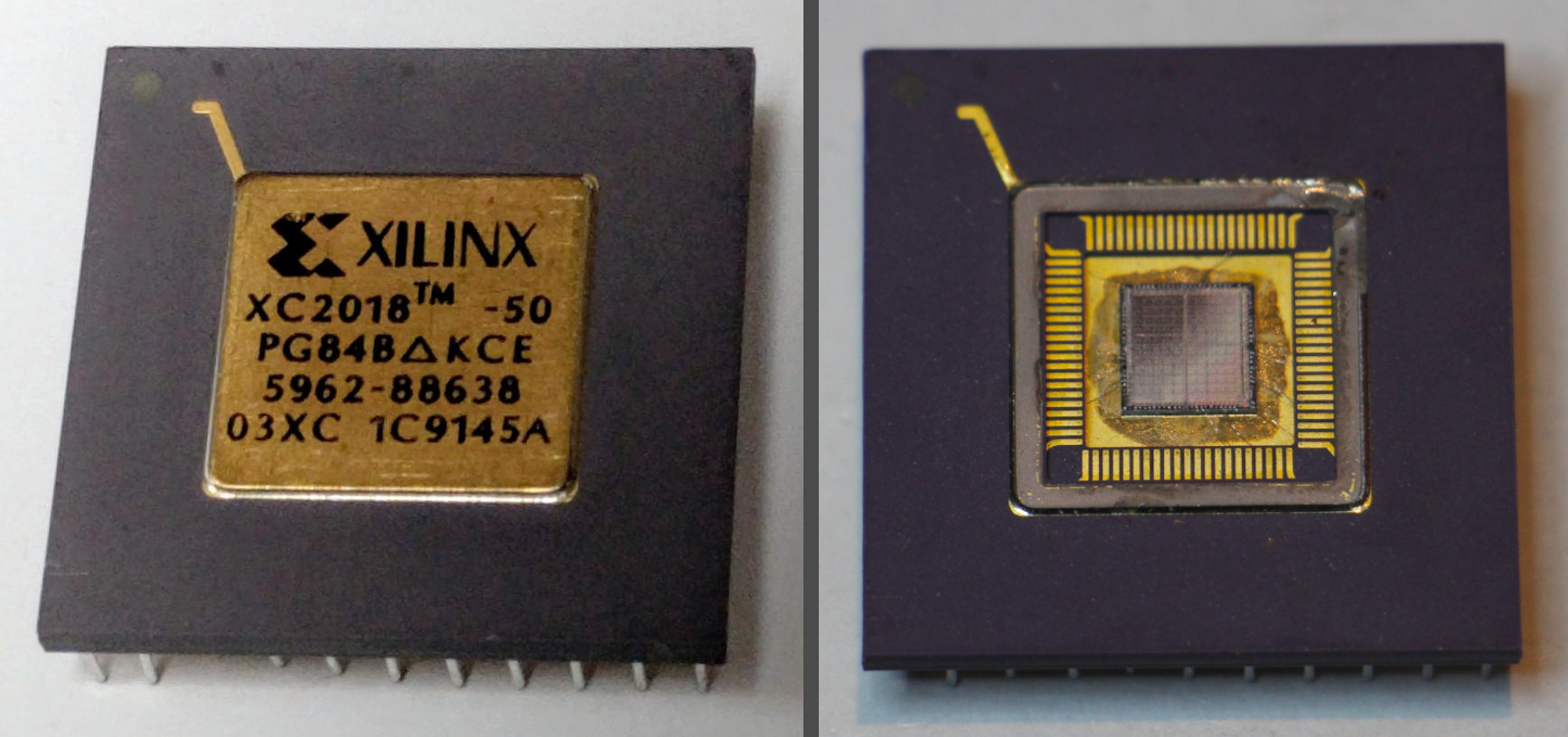

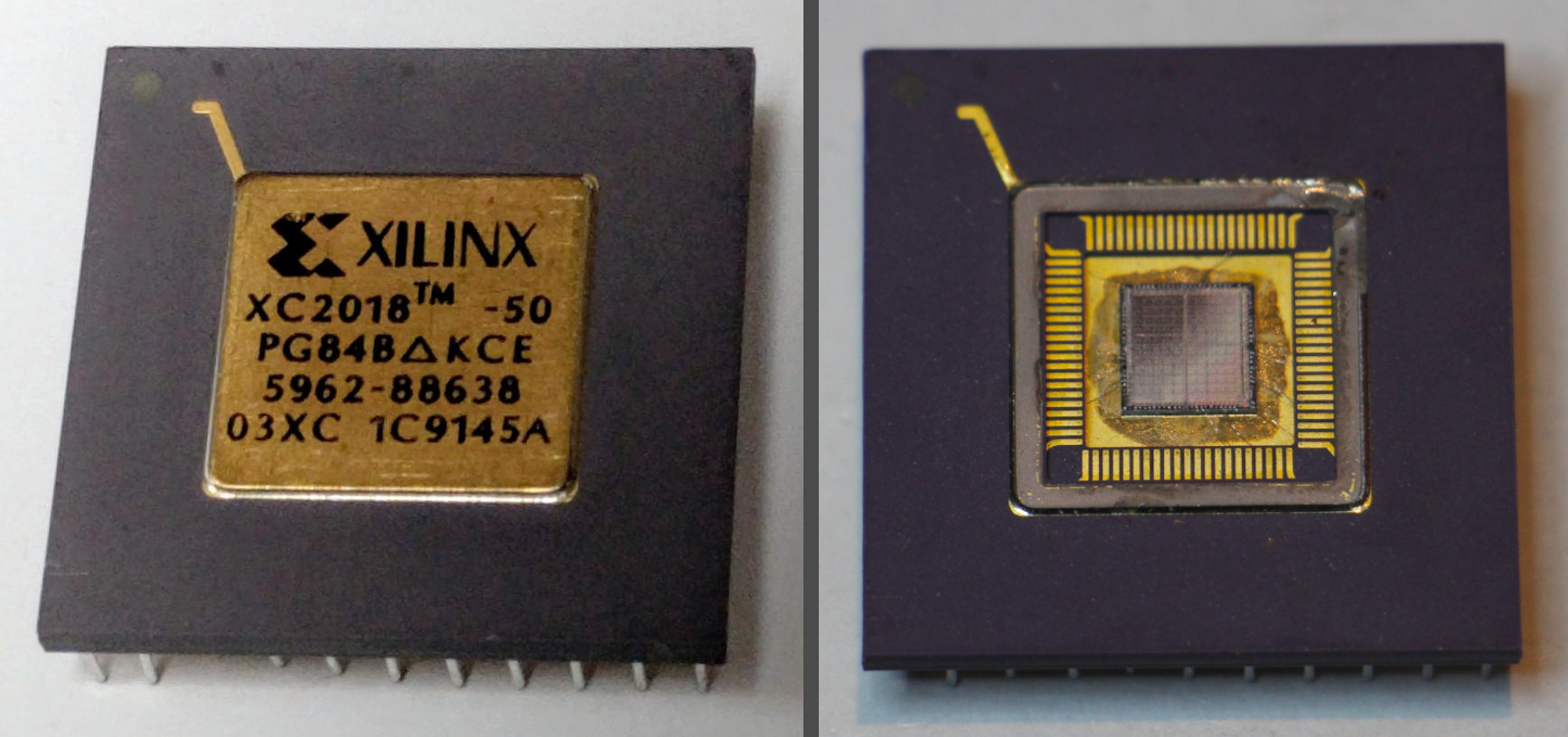

XC2018

Xilinx XC2018 ( ) 100 , , XC2064. , XC2064 64 , 1010, 88. XC2018 , .

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

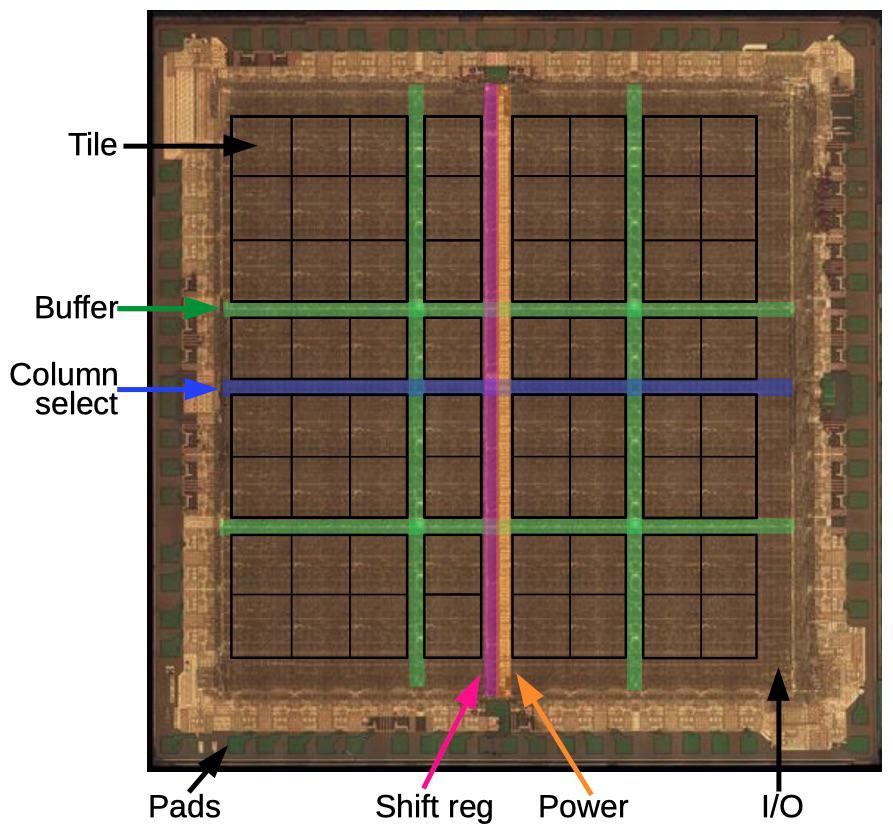

A continuación se muestra una foto del cristal XC2064. La parte principal de la FPGA es una matriz de bloques de 8x8, cada uno de los cuales contiene un bloque lógico y circuitos circundantes. Aunque el diagrama FPGA muestra bloques lógicos (CLB) separados de los diagramas de cableado de la entidad, en realidad este no es el caso. De hecho, cada bloque lógico y su entorno se implementa como un solo nodo, un mosaico. (Para ser precisos, el mosaico incluye conexiones en la parte superior e izquierda de cada CLB).

Diseño de bloque XC2064. Tomado de aquí: siliconpr0n .

Ubicados a lo largo de los lados del circuito integrado, los bloques de E / S proporcionan comunicación con el mundo exterior. Están conectados a los pines del cristal, que se muestran como pequeños cuadrados verdes, y están conectados a los pines de la caja del microcircuito. Hay tampones en el dado (verde): dos verticales y dos horizontales. Estos búferes amplifican la señal que viaja una gran distancia a través del chip y reducen la latencia. El registro de desplazamiento vertical (rosa) y la cadena de búsqueda de columna horizontal se utilizan para cargar el flujo de bits en el chip, como se muestra a continuación.

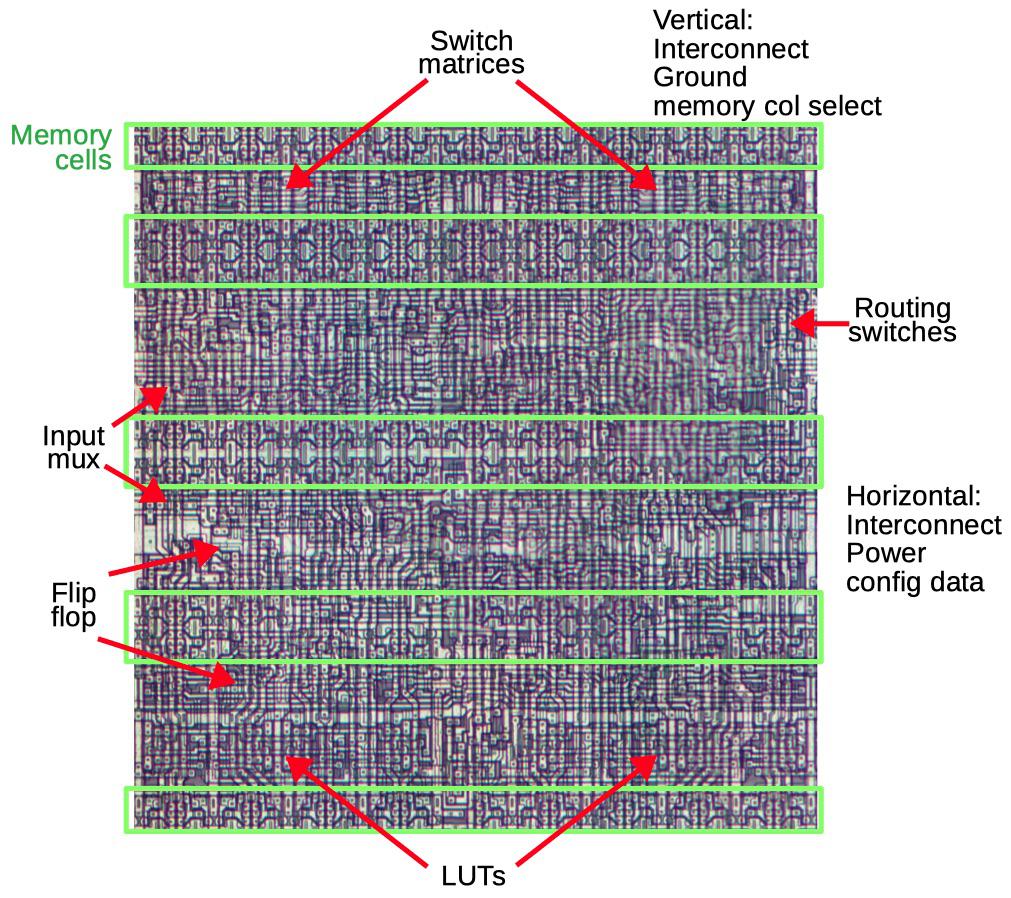

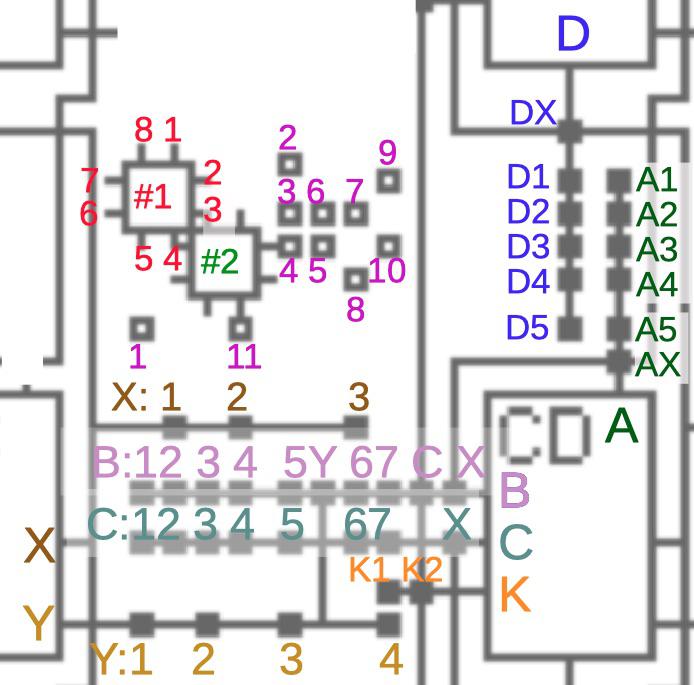

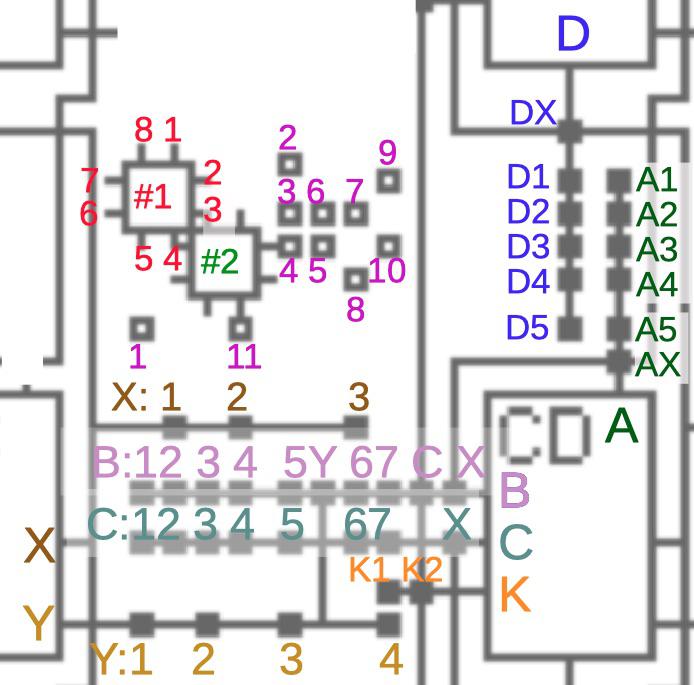

Dentro de los azulejos

La siguiente figura muestra la estructura de un mosaico XC2064, el chip contiene 64 de estos mosaicos empaquetados en un dado. Aproximadamente el 40% de cada mosaico está ocupado por celdas de memoria (mostradas en verde) que almacenan bits de configuración. El tercio superior (aproximadamente) del mosaico contiene los diagramas de conexión: dos matrices de conmutadores y varios conmutadores de enlace individuales. A continuación se muestra el bloque lógico. La parte principal del bloque lógico es el multiplexor de entrada, el flip-flop y la tabla de búsqueda. La loseta está conectada a los vecinos a través de líneas de comunicación horizontales y verticales, y también está conectada a los rieles de energía y tierra. Los bits de datos de configuración ingresan a las ubicaciones de la memoria horizontalmente y las señales verticales seleccionan una columna específica para cargar.

Un mosaico FPGA que muestra importantes nodos funcionales

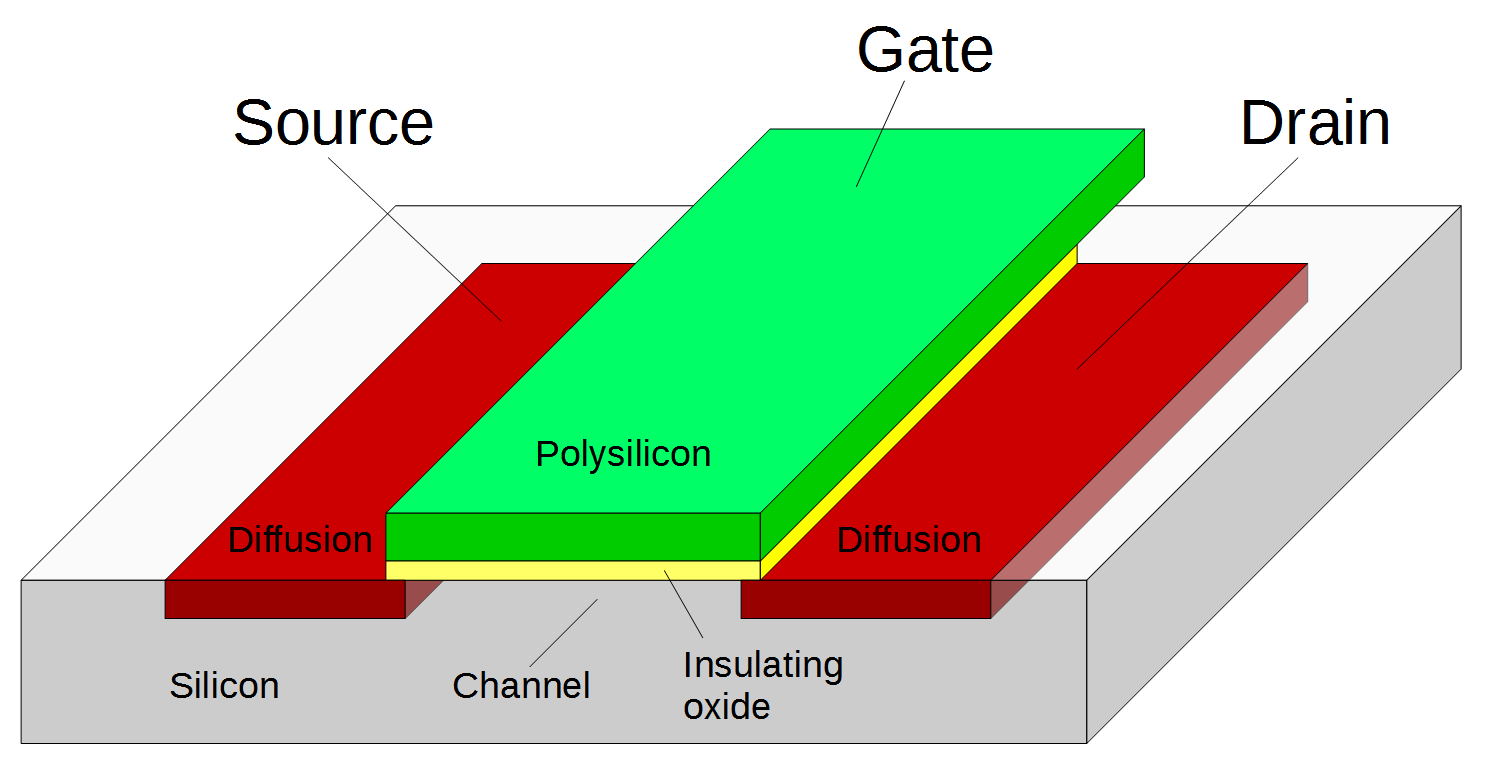

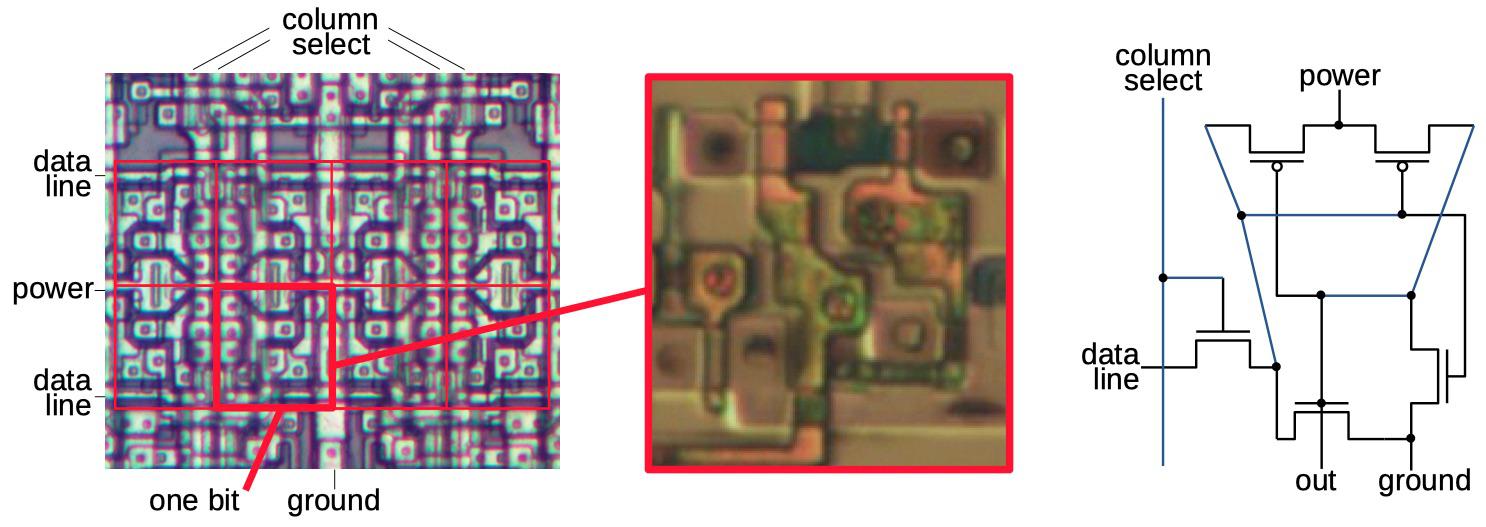

Transistores

FPGA se implementa en lógica CMOS (CMOS), construida a partir de transistores NMOS y PMOS. Los transistores juegan dos roles principales en los FPGA. Primero, los elementos lógicos se forman a partir de sus combinaciones. En segundo lugar, los transistores se utilizan como conmutadores a través de los cuales pasa una señal, por ejemplo, para formar conexiones entre bloques. Un transistor que desempeña esta función se denomina transistor pasante. La siguiente figura muestra la estructura básica de un MOSFET. Dos secciones de silicio se dopan con impurezas para crear un drenaje y una fuente. Entre ellos hay una puerta que enciende y apaga el transistor y controla la corriente entre el drenaje y la fuente. El obturador está hecho de un tipo especial de silicio llamado polisilicio, aislado del silicio que se encuentra debajo por una fina capa de óxido. Sobre él, hay dos capas de metalización, que proporcionan conexiones de circuito.

Estructura del MOSFET

En la foto del cristal, podemos observar cómo se ve el transistor bajo un microscopio. La puerta de polisilicio es una línea serpenteante entre dos regiones dopadas de silicio. Los círculos son vías que conectan el silicio y la capa de metal (que se elimina en esta foto).

MOSFET FPGA

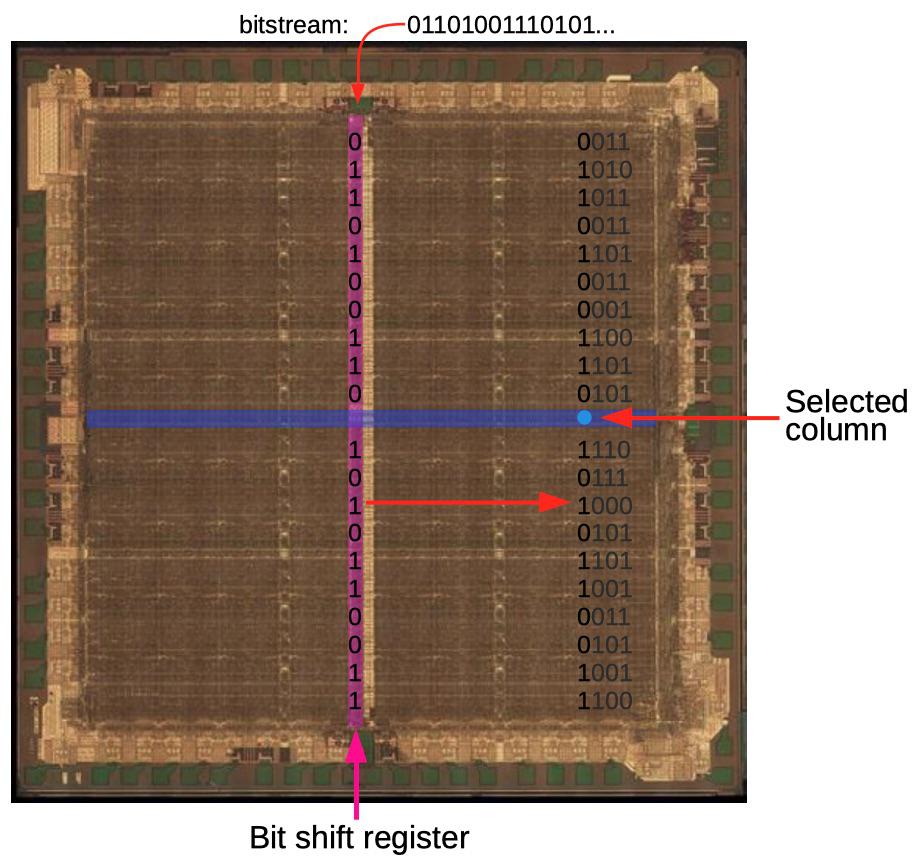

Bitstream y memoria de configuración

La información de configuración en el XC2064 se almacena en las ubicaciones de la memoria de configuración. La FPGA no usa memoria de bloque para esto, en cambio, la memoria de configuración se distribuye por todo el cristal en forma de cuadrícula de 160x71, cada bit se coloca al lado del circuito que controla. La siguiente figura muestra el flujo de bits de configuración cargado en la FPGA. El flujo de bits se carga en el registro de desplazamiento que va en el medio del chip (rosa). Una vez que se cargan 71 bits en el registro de desplazamiento, el circuito de búsqueda de columna (azul) selecciona la columna de memoria deseada y los bits se cargan en la columna en paralelo. Luego, los siguientes 71 bits se cargan en el registro de desplazamiento y se selecciona la siguiente columna a la izquierda. El proceso se repite para las 160 columnas de la FPGA y todo el flujo de bits se carga en la FPGA. El uso de un registro de desplazamiento elimina la necesidad de grandes circuitos de direccionamiento de memoria.

Cómo se carga el flujo de bits en la FPGA. Los bits se muestran de forma convencional, el almacenamiento real de bits es mucho más denso. Las tres columnas de la derecha ya se han cargado y la cuarta se está cargando. La foto del cristal se toma de aquí: siliconpr0n .

Lo importante es que el flujo de bits se distribuye por el chip exactamente en el orden en que aparecen los bits en el archivo: el empaquetado de los bits en el flujo de bits corresponde a su ubicación física en el chip. Como se mostrará a continuación, cada bit se almacena en el FPGA junto al circuito que controla. por lo tanto, el formato de archivo de flujo de bits se determina directamente por la ubicación de los circuitos de hardware. Por ejemplo, si hay un espacio entre mosaicos y hay un búfer en él, el mismo espacio estará en el flujo de bits. La estructura del flujo de bits no depende de abstracciones de software como campos en tablas de datos o bloques de configuración. Comprender el flujo de bits requiere pensar en términos de hardware, no de software

Bitstream

, (.RBT) , .

, .

, .

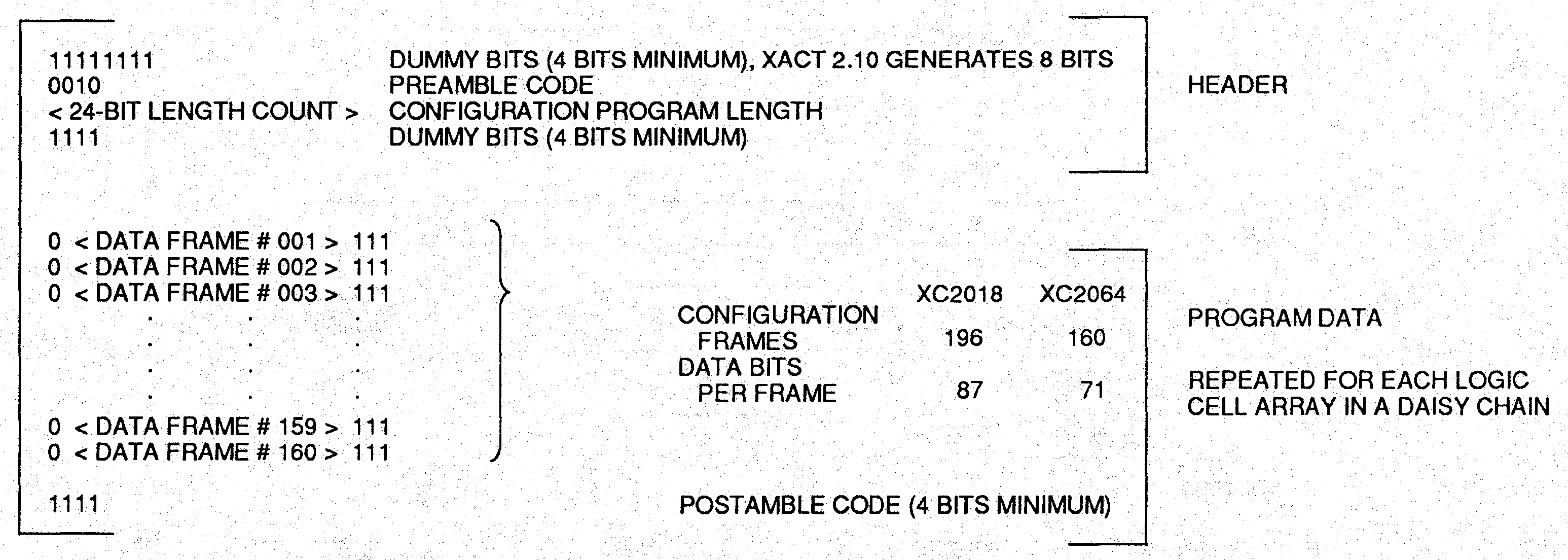

Cada bit de la memoria de configuración se implementa como se muestra a continuación. Cada celda de memoria consta de dos inversores conectados en un bucle. dicho circuito tiene dos estados estables y puede almacenar un bit: o el inversor superior está en el estado 1 y el inversor inferior está en el estado 0, o viceversa. Para escribir en la celda, se activa el transistor de paso de la izquierda, pasando la señal. La señal en la línea de datos simplemente tira del inversor escribiendo el bit requerido. (También puede leer los datos de configuración usando el mismo renglón). La salida Q y la Q invertida controlan una función específica en la FPGA, como cerrar una interconexión, recuperar un bit de una tabla de búsqueda o controlar un disparador. En la mayoría de los casos, solo se utiliza la salida Q.

Celda SRAM

(SRAM). , RAM, , , SRAM. , 5T SRAM.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

Diagrama de un bit de memoria de configuración, de la documentación.

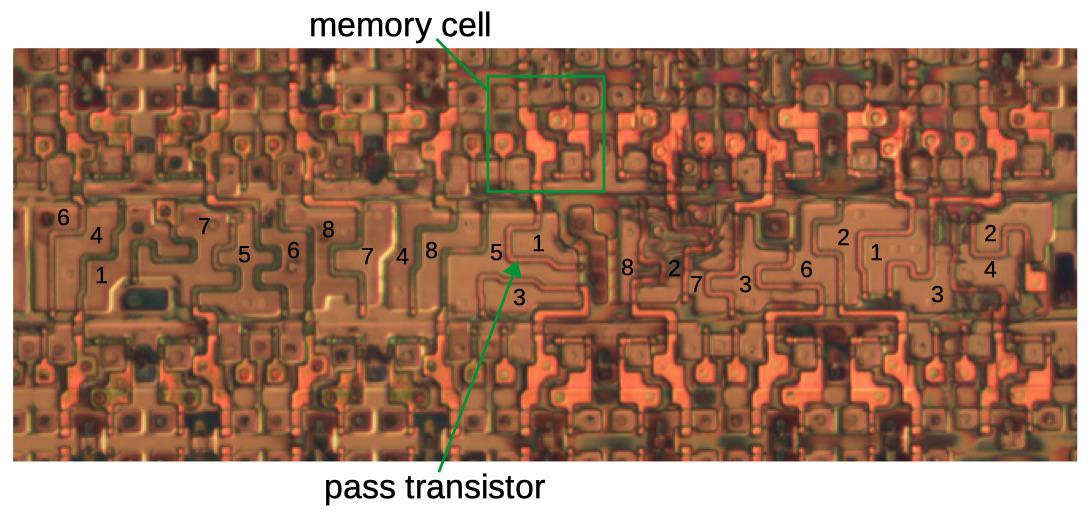

La siguiente figura muestra la estructura física de las células de memoria. La foto de la izquierda muestra 8 celdas de memoria, una de las cuales está resaltada. Cada línea de datos horizontal está conectada a todas las ubicaciones de memoria en la fila. Cada línea de búsqueda de columna selecciona todas las ubicaciones de memoria en la columna, lo que permite la escritura. La foto del medio muestra secciones de silicio y polisilicio para una celda de memoria. Las capas de metal se han eliminado para exponer los transistores que se encuentran debajo. Las capas de metalización conectan transistores, círculos en la foto, estas son conexiones, vías, entre silicio o polisilicio y metal. El diagrama muestra cómo se conectan cinco transistores, la ubicación de los elementos en el diagrama corresponde a su ubicación en la foto. Dos pares de transistores forman los inversores CMOS, con un transistor de paso en la parte inferior izquierda que proporciona acceso a la celda.

, . — . , . . : siliconpr0n.

Como se explicó anteriormente, FPGA implementa funciones lógicas arbitrarias usando tablas de búsqueda. La siguiente figura muestra cómo se implementa la tabla de búsqueda en XC2064. Los ocho valores de la izquierda se almacenan en ocho ubicaciones de memoria. Cuatro multiplexores seleccionan uno de cada par de valores, dependiendo del valor en la entrada A, si A = 0, se selecciona el valor superior, si A = 1, entonces el inferior. Luego, el multiplexor grande elige uno de cuatro valores basados en las señales B y C. El resultado será un valor específico, en este caso A XOR B XOR C. Podemos hacer cualquier función lógica si sustituimos diferentes valores en la tabla.

Implementación de XOR en la tabla de búsqueda.

Cada multiplexor se implementa con transistores de paso. Dependiendo de las señales de control, uno de los transistores de paso se activa, pasando datos de entrada a salida. La siguiente figura muestra una parte de la cadena LUT, con dos bits multiplexados. A la derecha hay dos ubicaciones de memoria. Cada bit pasa a través del inversor, se amplifica y pasa a través de los transistores de paso del multiplexor en el medio, seleccionando uno de estos bits.

Vista de las redes que implementan la LUT. Tomado de siliconpr0n.

Desencadenar

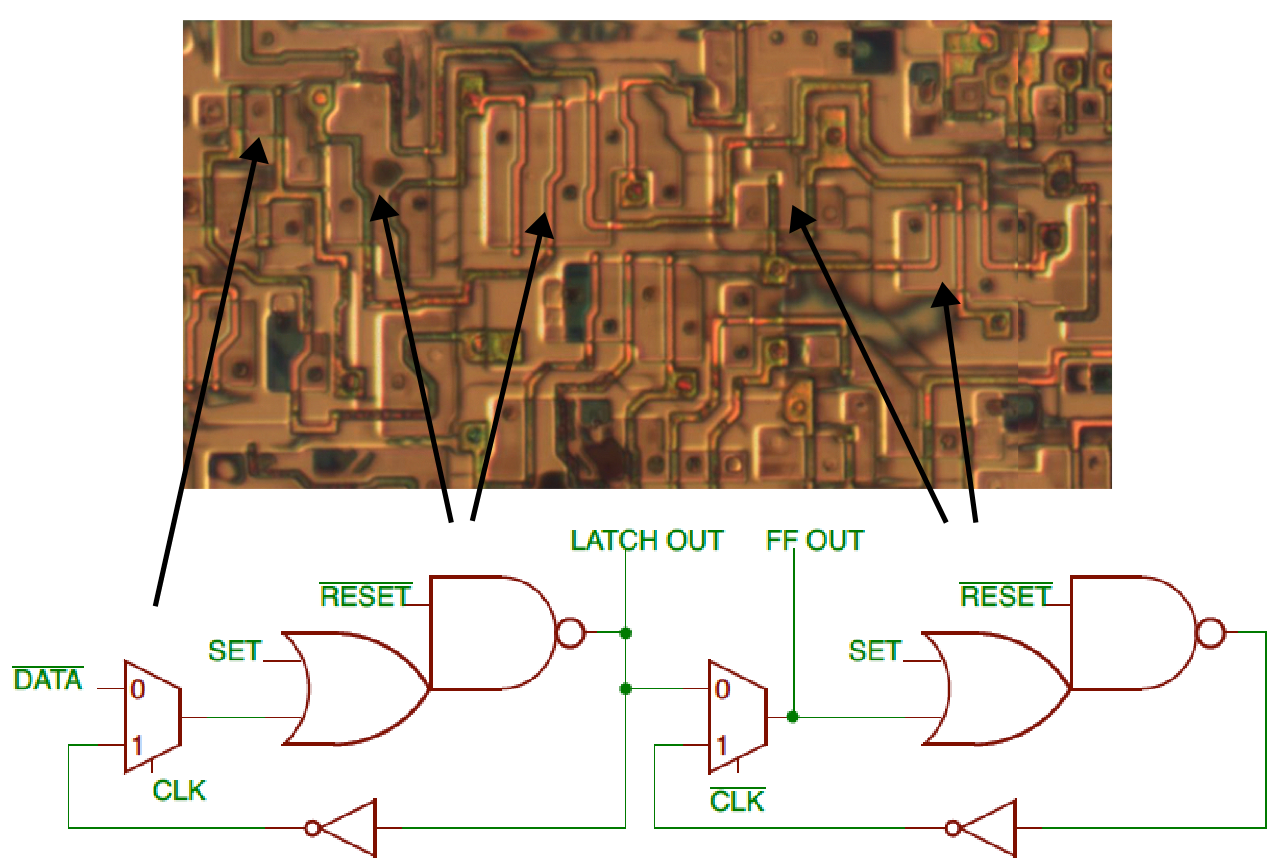

Cada CLB contiene un flip-flop que permite a la FPGA implementar pestillos, máquinas de estado y otras redes con estado. La siguiente figura muestra una implementación de disparador (algo inusual). Ella usa el siguiente esquema. Cuando la señal del reloj es cero, el primer mux pasa los datos al primer pestillo, que almacena el valor. El bit se invierte dos veces, cuando pasa a través de las puertas OR, NAND y del inversor, y como resultado permanece igual. además, el segundo multiplexor de pestillo recibe el bit del primer pestillo cuando el reloj sube a 1 (tenga en cuenta que el reloj está invertido). Este valor es la salida del flip-flop. Cuando la señal de reloj se establece en 0, el multiplexor secundario cierra el bucle bloqueando el bit. Por lo tanto, el disparador es sensible al borde de la señal,enganchando el valor en el borde anterior de la señal del reloj. Establecer y restablecer líneas establecer y restablecer el flip-flop.

. OR-NAND : siliconpr0n.

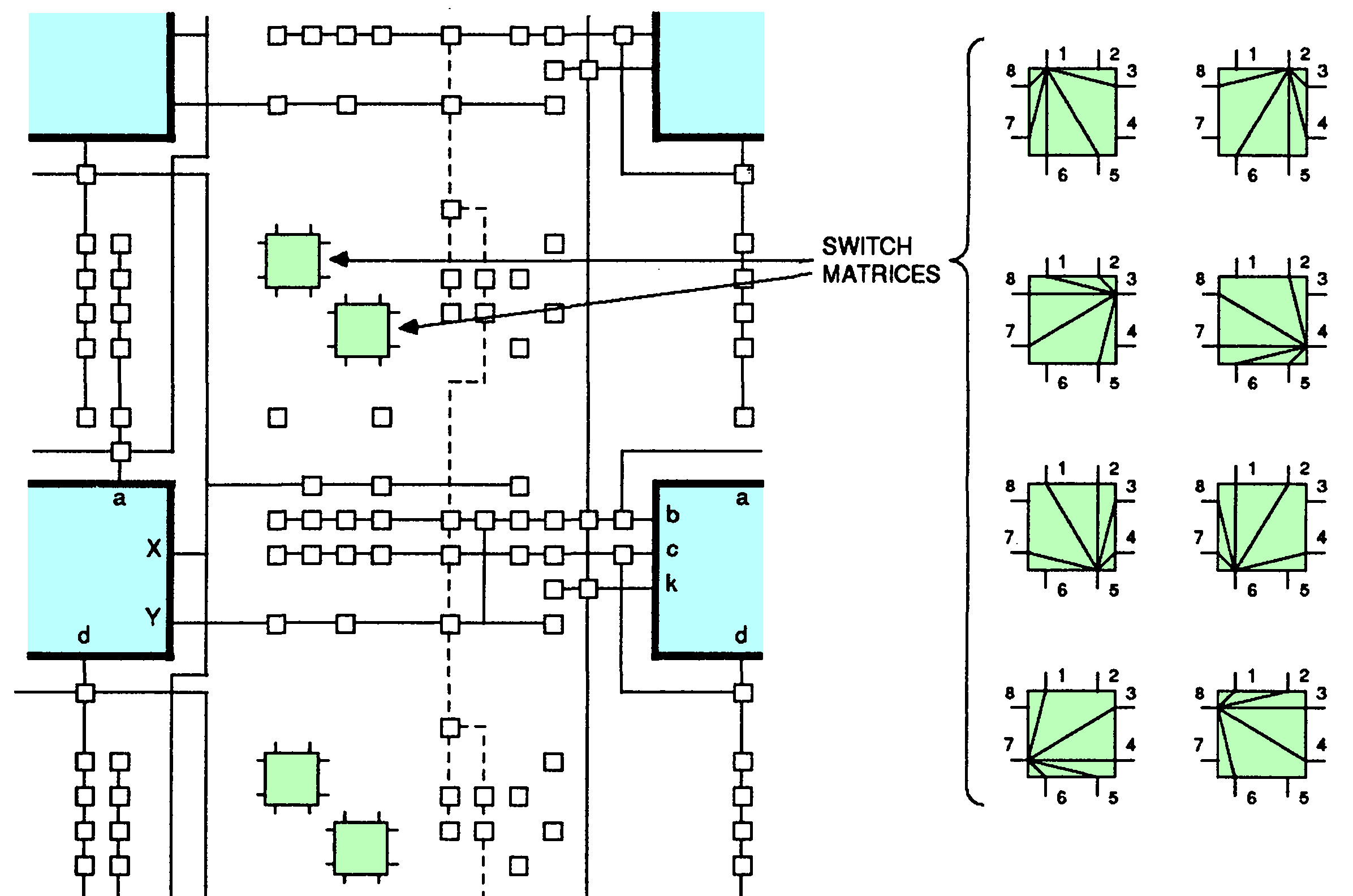

La matriz de conmutación es un elemento de interconexión importante. Cada interruptor tiene 8 pines (dos en cada lado) y puede conectarlos de casi cualquier manera. Las señales se pueden desenvolver, dividir e intersecar con más flexibilidad que en los nodos de interconexión individuales. La siguiente figura muestra una parte de la red de interconexión entre los cuatro CLB (azul). Las matrices de conmutación (verde) se pueden conectar en cualquier combinación de conexiones en el lado derecho. Tenga en cuenta que cada pin se puede conectar a otros pines en una cantidad de 5 a 7 piezas. Por ejemplo, el pin 1 se puede conectar al pin 3, pero no a los pines 2 y 4. Esto hace que la matriz esté casi completa, con 20 conexiones posibles en lugar de 28.

Tomado de aquí: Libro de datos de matriz de puerta programable Xilinx , fig. 7b.

La matriz de conmutación está formada por filas de transistores de paso controlados por las celdas de memoria por encima y por debajo de ellas. Los dos lados del transistor son dos pines de la matriz de conmutación que se pueden conectar mediante el transistor. Entonces cada matriz tiene 20 bits de control, dos matrices por mosaico nos da 40 bits por mosaico. La foto de abajo muestra una celda de memoria conectada a la puerta ondulada del transistor debajo. Este transistor proporciona la conexión entre la patilla 5 y la patilla 1. Así, el bit en el flujo de bits correspondiente a esta ubicación de memoria controla la conexión entre las patillas 5 y 1. De manera similar, otras celdas de memoria y sus transistores asociados controlan otras conexiones. Tenga en cuenta también que el orden de estas conexiones no sigue ningún patrón en particular, como resultado,la correspondencia entre los bits del flujo de bits y los pines del conmutador parece aleatoria.

Matriz de conmutación

20 . 18 , .

Implementación de una matriz de conexiones de 8 derivaciones. Las regiones de silicio están designadas por los números de sus correspondientes pines. Se han eliminado las capas de metal que conectan los cables correspondientes a los transistores. Tomado de siliconpr0n.

Conexiones de entrada

Las entradas CLB utilizan un esquema de codificación de flujo de bits diferente, que se explica por su implementación de hardware. En la imagen de abajo, los ocho nodos elipsados son entradas potenciales al CLB llamado DD. Solo se puede configurar un nodo (máximo) como entrada, ya que conectar dos señales a una entrada puede acortarlas.

Selección de entrada. Las ocho entradas encerradas en un círculo verde son entradas DD potenciales, solo una de ellas puede seleccionarse.

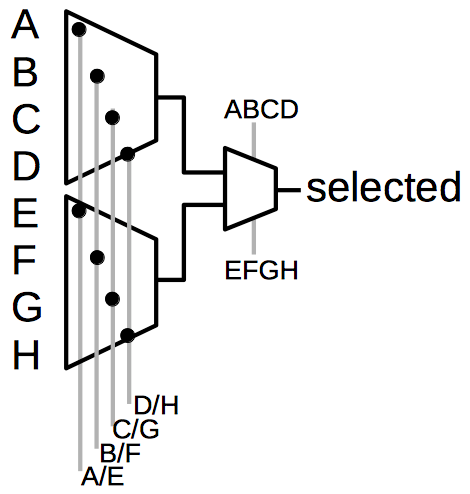

La entrada requerida es seleccionada por el multiplexor. Una solución sencilla sería utilizar un multiplexor de 8 entradas con tres bits de control eligiendo una de las 8 señales. Otra solución sencilla sería utilizar 8 transistores de paso, cada uno con su propia señal de control, uno de los cuales selecciona la señal requerida. Sin embargo, la FPGA usa un enfoque híbrido que elimina la necesidad de un decodificador en el primer caso, pero requiere 5 señales de control en lugar de las 8 requeridas en el segundo enfoque.

La FPGA usa multiplexores para seleccionar una de las ocho entradas.

El diagrama de la figura anterior muestra el multiplexor de dos capas utilizado en la FPGA. En la primera etapa, se activa una de las señales de control. En la segunda etapa, la señal alta o baja se selecciona y se aplica a la salida. Por ejemplo, suponga que la señal de control B / F se aplica a la primera etapa y ABCD a la segunda etapa, la entrada B será la única que vaya a la salida. Es decir, seleccionar una de las ocho entradas requiere 5 bits en el flujo de bits y usa 5 ubicaciones de memoria.

Multiplexor de entrada CLB

CLB. EFGH ABCD, . -, CLB 6 10 , , . , , , , . , , 6 , . , , .

Conclusión

El XC2064 utiliza una variedad de redes altamente optimizadas para implementar bloques lógicos e interconexión de redes. Estas cadenas deben estar bien empaquetadas para encajar en el cristal. Aun así, el XC2064 era un chip muy grande, más grande que el microprocesador en ese momento, y era difícil de fabricar, costando cientos de dólares. En comparación con los FPGA modernos, el XC2064 tiene una cantidad absurdamente pequeña de celdas, pero incluso eso fue el comienzo de una nueva y revolucionaria línea de productos.

Dos conceptos son clave para comprender el flujo de bits XC2064. Primero, la FPGA se implementa sobre la base de 64 mosaicos, bloques repetidos que combinan bloques lógicos e interconexiones. Aunque se describe que la FPGA tiene bloques lógicos rodeados de interconexiones, no se implementa de esa manera. El segundo concepto es que el flujo de bits no se basa en abstracciones, sino que mapea directamente el empaquetado bidimensional de las celdas de memoria FPGA. Por lo tanto, el flujo de bits solo tiene sentido si está considerando la estructura física de la FPGA.

Nota

, XC2064 (. 11), CLB . , , 20% , . — -, . , . .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

He anunciado mi última publicación en Twitter, así que sigue a kenshirriff . También tengo una fuente RSS . Gracias a John McMaster, Tim Ansell y Philip Freidin por las discusiones.