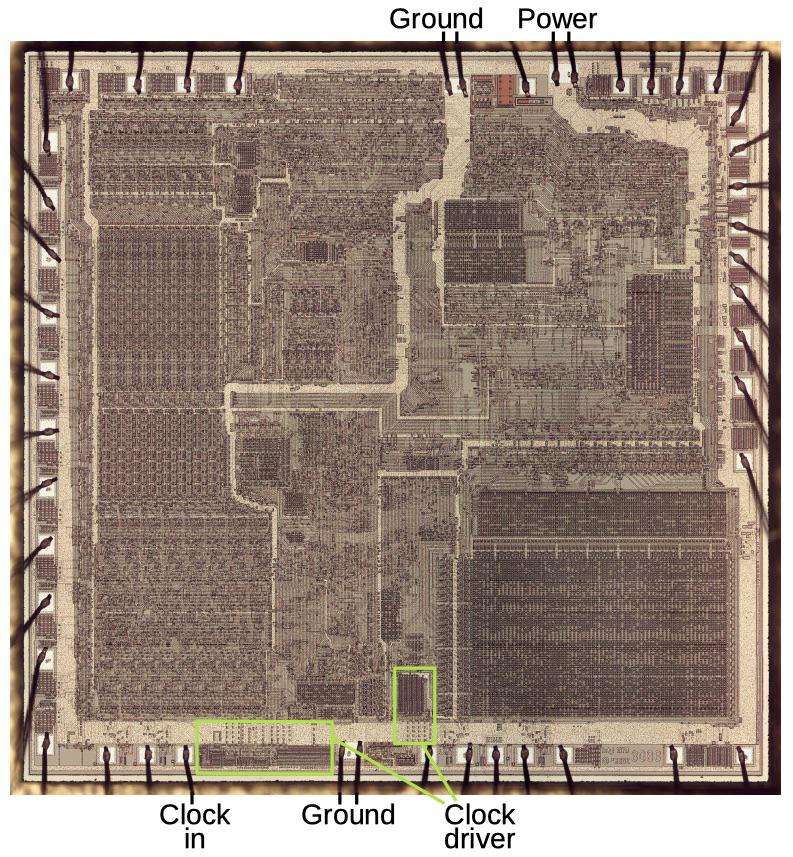

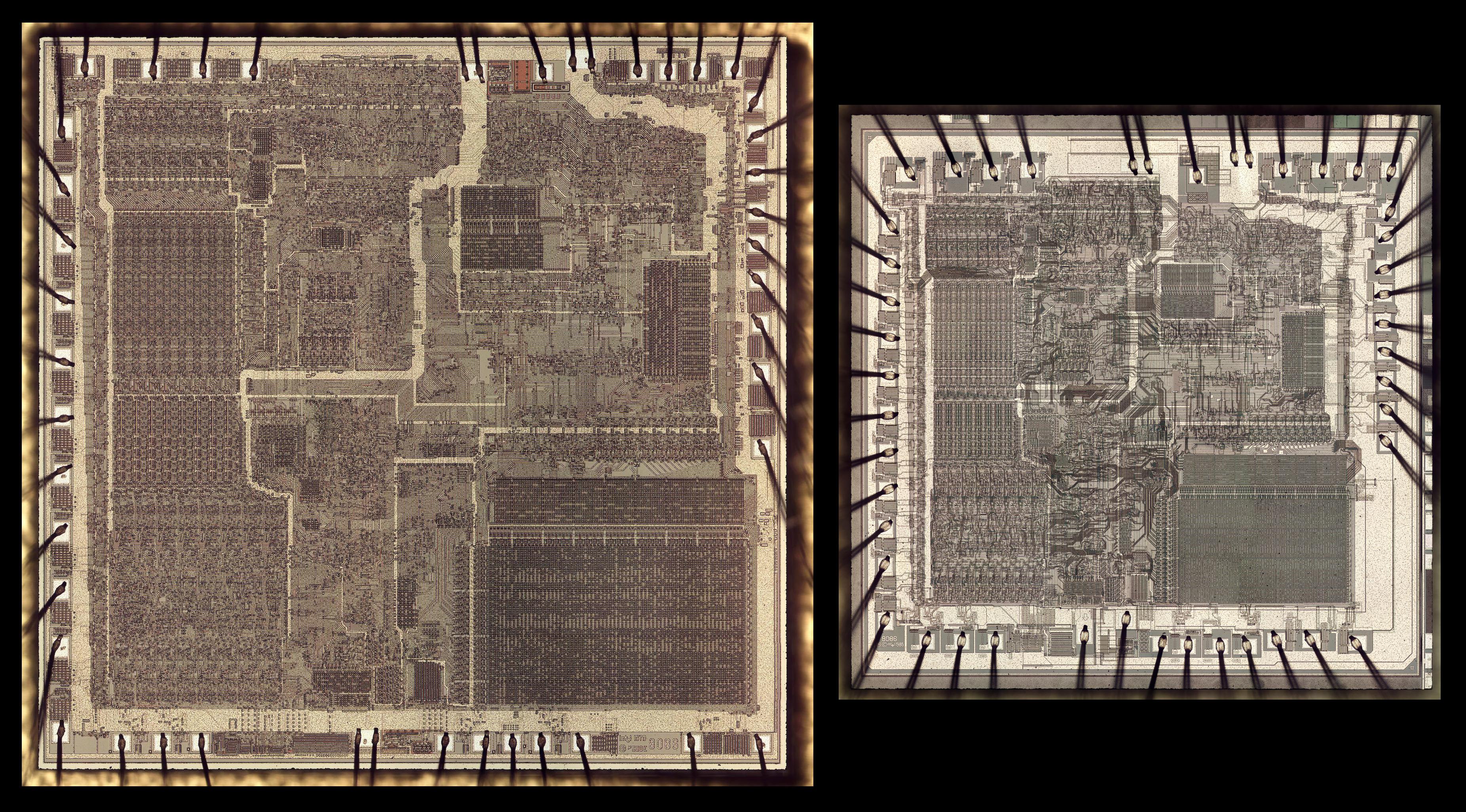

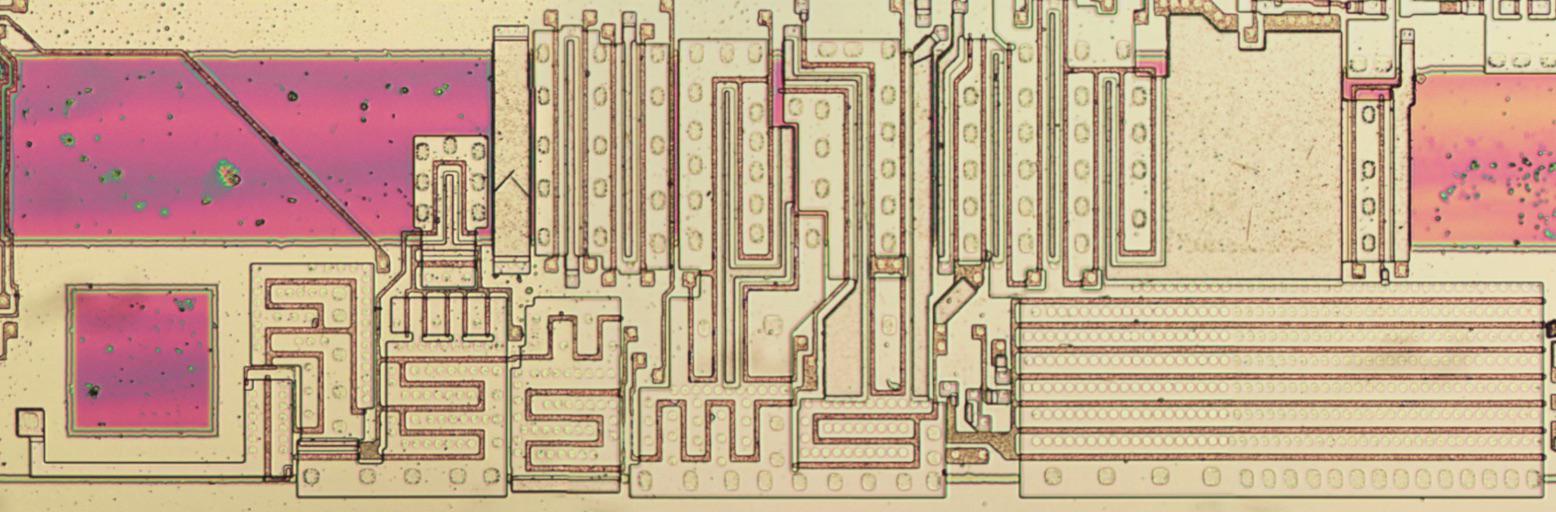

La foto de abajo muestra un cristal 8086 bajo un microscopio. Una capa de metal es visible en la parte superior del chip, debajo de la cual se esconden un sustrato de silicio y una capa de polisilicio con conductores. A lo largo del exterior del perímetro del cristal, un pequeño enlace de alambre conecta las almohadillas del cristal con las patas exteriores. En el 8086, la almohadilla de alimentación está en la parte superior y las almohadillas de tierra están arriba y abajo. Cada uno de ellos tiene dos alambres para soldar alambres, lo que duplica la corriente soportada. Los caminos de metal anchos son visibles que se extienden desde las plataformas de alimentación y de tierra. Distribuyen la energía a través del chip.

Foto del cristal 8086, donde puede ver la ubicación de la fuente de alimentación (arriba) y los contactos de tierra (arriba y abajo). Los circuitos de temporización se encuentran en la parte inferior.

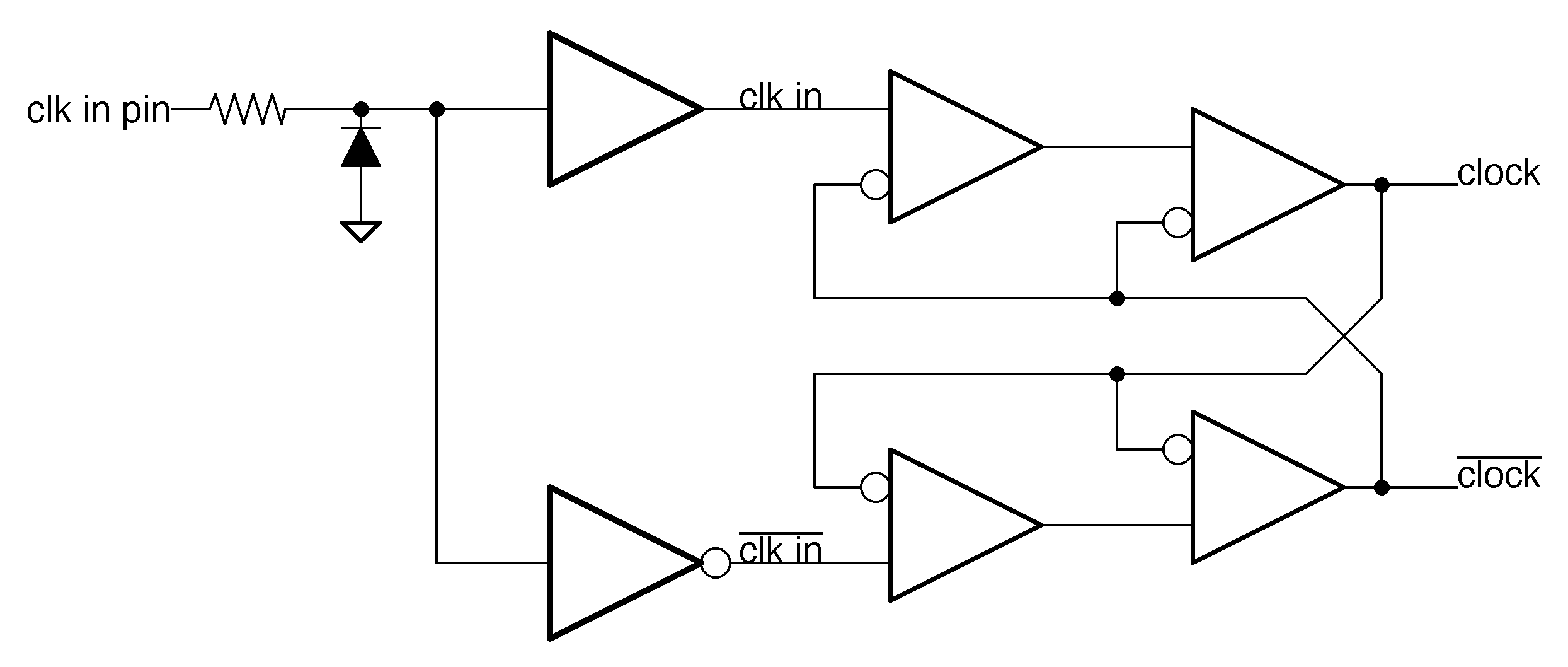

Hay dos señales de reloj interno responsables de la sincronización en el 8086. Un oscilador externo alimenta señales de reloj al 8086 a través de la almohadilla de reloj de entrada a continuación. El generador de reloj interno proporciona dos señales de reloj de alta corriente basadas en señales externas. Tenga en cuenta que el controlador del reloj ocupa una gran superficie en el chip.

En este artículo, describiré cómo el 8086 redirige la energía y las señales de reloj a través del chip, y cómo el circuito de reloj genera los pulsos de reloj requeridos.

Distribución de poder

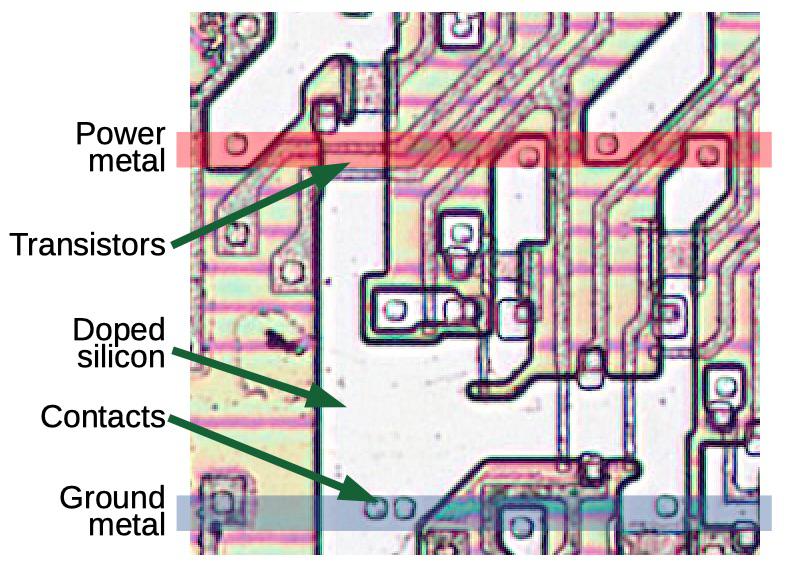

8086 consta de tres capas, cada una de las cuales puede alojar conductores. La capa de metal en la parte superior es la mejor para esto debido a la baja resistencia del metal. Debajo del metal hay una capa conductora de polisilicio hecha de un tipo especial de silicio. La resistencia del polisilicio es más alta que la del metal, pero aún puede usarse para transmitir señales a través del chip. Los transistores se forman sobre el sustrato de silicio. La resistencia del silicio es relativamente alta, por lo que solo se usa para transmitir señales a distancias cortas, por ejemplo, dentro de una puerta.

La distribución de energía en un chip como el 8086 es un rompecabezas topológico. Debido a su baja resistencia, la capa de metal sigue siendo la única capa prácticamente útil para el cableado de energía y tierra. Casi todas las puertas del chip deben recibir alimentación y tierra. Y dado que el chip tiene una capa de metal, la potencia y la tierra no pueden cruzarse.

Casi todas las puertas del chip necesitan energía y tierra porque la puerta MOS estándar requiere tierra para su red desplegable y energía para su resistencia pull-up. Sin embargo, existen algunas excepciones. 8086 usa puertas lógicas dinámicas, especialmente en ALU, para velocidad. Estas puertas son atraídas hacia arriba por la señal de sincronización, por lo que no necesitan una fuente de alimentación directa. El 8086 también usa múltiples puertas XOR en los transistores de paso, que son empujados hacia abajo por la señal entrante, por lo que no necesitan tierra.

La ROM de microcódigo forma una gran sección del chip que no necesita energía, solo tierra. Esto se debe a que cada fila de ROM se implementa como una puerta NOR muy grande, y la potencia que la impulsa se encuentra en el borde derecho. Por lo tanto, todas las puertas de la ROM tienen alimentación y tierra, aunque parece que la ROM carece de conexión de alimentación.

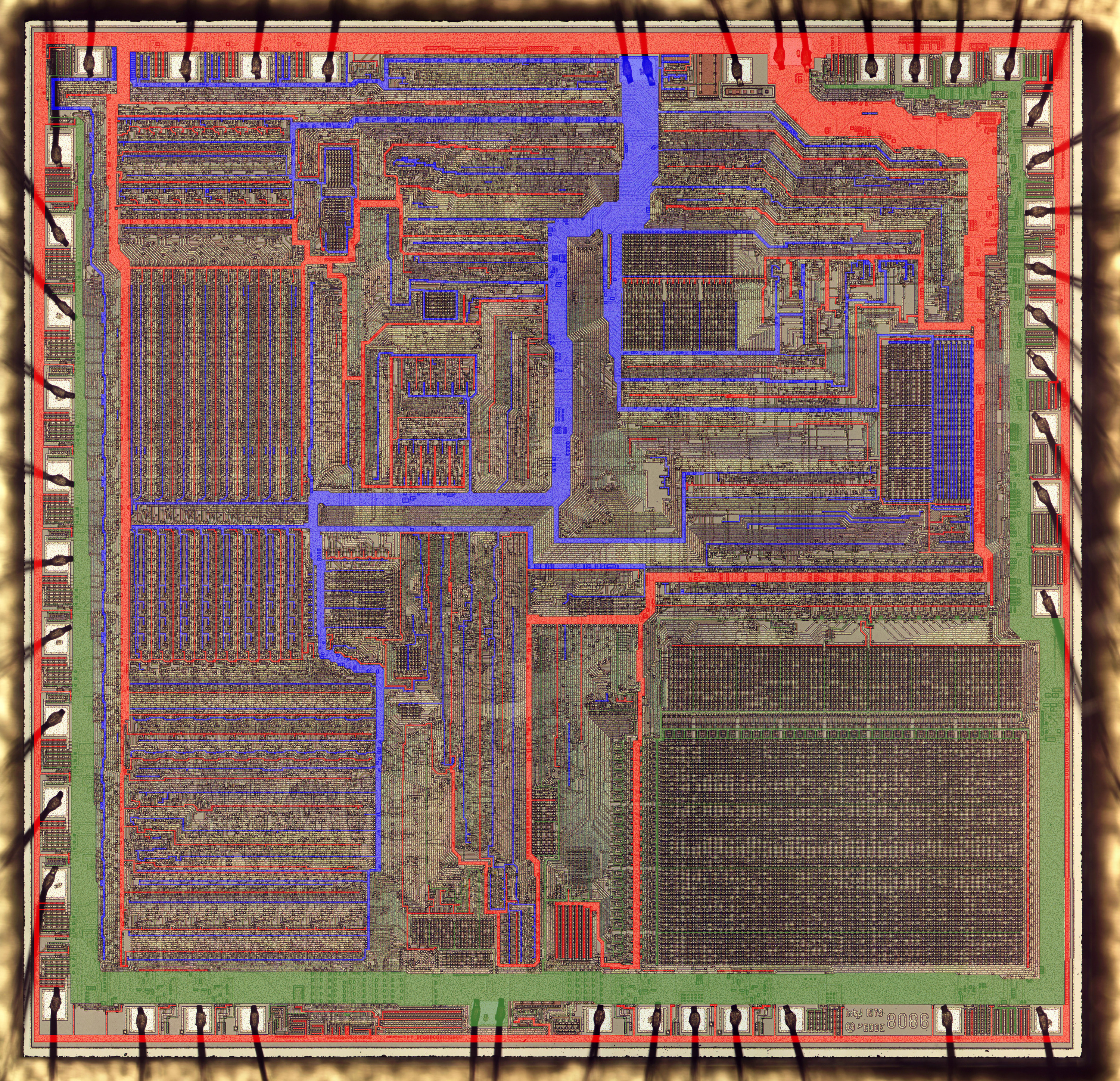

El siguiente diagrama muestra los conductores metálicos en el 8086. La fuente de alimentación conectada al pin de alimentación en la parte superior se muestra en rojo. Una poderosa rama de alimento desciende hacia la derecha y luego se divide en muchas ramas. La energía también corre a lo largo del borde de todo el chip, proporcionando energía a los pines de E / S.

Con los circuitos integrados, a menudo sucede que la alimentación y la tierra están ubicadas en esquinas opuestas o en lados opuestos del chip. Esta disposición facilita el enrutamiento de pistas eléctricas y terrestres que no se cruzan entre sí. El 8086 tiene una posición ligeramente inusual de alimentación y tierra en pines diagonalmente opuestos, y la segunda tierra más cerca del pin de alimentación. Las redes eléctricas y las tierras del chip se ramifican como árboles. Estas redes se ramifican y, como dedos entrelazados, llegan a todas las partes del chip.

Energía (rojo) y tierra (azul, verde) en la capa de metal del chip

Hay dos contactos de tierra. Las pistas marcadas en azul se conectan al pin de tierra superior y las verdes a la parte inferior. Los caminos de tierra marcados en azul muestran una gruesa ramificación hacia abajo a través del centro del chip y que se ramifica de forma intrincada en todas las direcciones. Los carriles verdes corren a lo largo de la parte inferior, los lados izquierdo y derecho del chip, soportando los pines de E / S y conectando a la ROM del microcódigo en la parte inferior derecha.

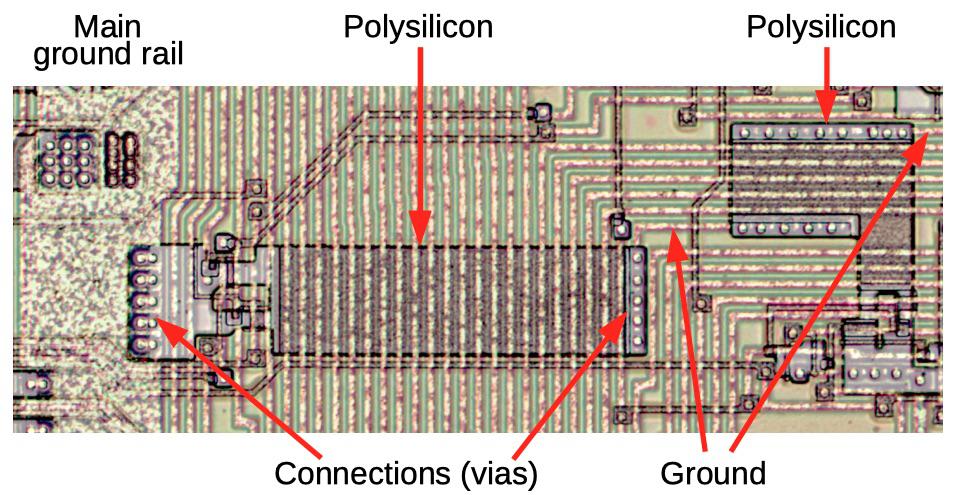

Al alejarse de la fuente de energía y acercarse a los puntos finales, los conductores de energía se vuelven más delgados y la corriente disminuye. Esto se puede ver en el conductor de alimentación a la dirección y los pines de datos a continuación. A la izquierda, debajo de los contactos, el conductor con el suelo es muy ancho, pero se estrecha gradualmente, yendo hacia la derecha. En otras palabras, a la izquierda, el conductor debe conducir corriente desde todos los contactos, y en el lado derecho, solo desde uno.

La conexión de los pines de dirección y datos a tierra es cada vez más delgada (el lado izquierdo del chip gira 90 °) La

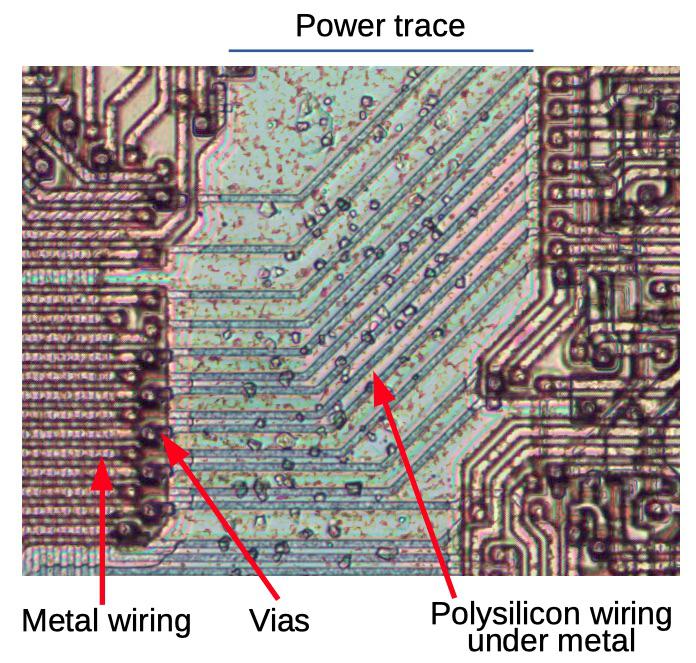

capa de metal se utiliza para transportar muchas señales, no solo energía y tierra. Debido a su baja impedancia, es la mejor capa de transmisión de señal. Sin embargo, el uso generalizado de conductores de potencia y de tierra limita las capacidades de la capa metálica. Para evitar el cruce, la mayoría de las rutas de señal en la capa de metal corren paralelas a las rutas de energía. Una capa de polisilicio debajo se usa para la transmisión de señal perpendicular. Pero, ¿qué sucede si un conductor de metal necesita cruzar una vía eléctrica o de tierra? La solución es sacarlo desde abajo [crossunder]. La señal desciende al nivel de polisilicio, cruza la pista y luego vuelve a subir, como se muestra a continuación.

Estos cruces de fondo se utilizan en muchos casos, no solo con alimentos. Sin embargo, la mayoría de las veces se trata de nutrición. Normalmente, los conductores metálicos se utilizan para transmitir señales en una dirección y los conductores de polisilicio se utilizan para transmitir señales en la perpendicular. En diferentes lugares del chip, estas direcciones cambian y dependen de la dirección dominante de transmisión de la señal. Por lo tanto, en su mayor parte, las señales viajan sin obstáculos. Y, sin embargo, a menudo tienen que saltar de una capa a otra.

Las señales en la capa de metal atraviesan las rutas de suministro desde abajo a través de una capa de polisilicio

Si la energía y la tierra se dirigen casi por completo a la capa de metal, en un par de lugares este circuito se interrumpe y las pistas que pasan por la parte inferior se utilizan para suministrar energía. Esto sucede con más frecuencia en las últimas secciones de las pistas, donde la corriente ya es baja. A continuación se muestra un ejemplo, donde el suelo pasa dos veces desde la parte inferior de la capa de metal utilizando conductores de polisilicio. Para reducir la resistencia, estas rutas de derivación se hacen mucho más anchas que las rutas de la señal y también usan silicio y polisilicio juntos. Los círculos pequeños son a través de contactos [vía] entre las capas de metal y polisilicio.

Foto compuesta que muestra rutas de derivación de tierra que atraviesan polisilicio debajo de las rutas de señal.

La capa de silicio juega un papel menor en el cableado de energía. En particular, muchas puertas se estiran para alcanzar la energía y el suelo desde el otro lado. La foto de abajo muestra las puertas 8086. Observe las grandes áreas de silicio dopado (blanco) que se extraen para alcanzar el suelo y los rieles eléctricos. Solo una pequeña fracción del silicio se usa para transistores, y todo lo demás parece una pérdida de espacio. Sin embargo, estas secciones vacías de silicio conectan las puertas a los conductores metálicos que suministran energía y tierra. Dado que el silicio tiene una resistencia relativamente alta, se utilizan áreas amplias para esto y las juntas se extienden en distancias cortas.

Las compuertas hechas con silicio dopado se pueden alargar para alcanzar los rieles de potencia y tierra. Para esta foto, se ha eliminado la capa de metal.

Después de que el 8086 se actualizó y se redujo físicamente, tuvo otros problemas de cableado de alimentación. Con la mejora de la tecnología de producción, Intel escaló los cristales , dejó los circuitos iguales, pero los redujo proporcionalmente. Desafortunadamente, reducir el tamaño de las pistas de la fuente de alimentación también reduce la corriente máxima. Para resolver este problema, se reforzaron las rutas de alimentación alrededor del chip y se redujeron los circuitos internos y el cableado. Esto se puede ver en la foto a continuación; por ejemplo, hay muchas más pistas de potencia en la esquina inferior derecha del 8086 más pequeño.

Dos versiones del 8086 en la misma escala. El cristal de la derecha es una versión posterior, de tamaño reducido.

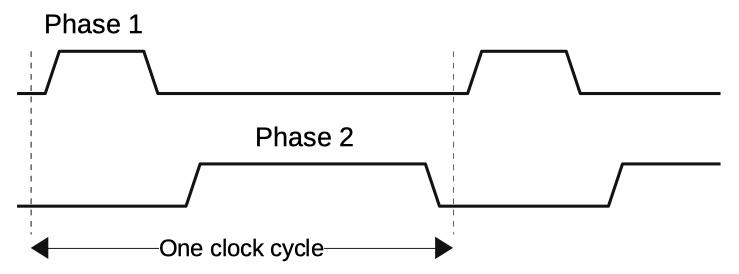

Casi todas las computadoras usan señales de reloj para controlar la sincronización del procesador. El 8086, como muchos microprocesadores, utiliza internamente un controlador de reloj de dos fases. Un controlador de reloj bifásico tiene dos relojes: cuando el primero es alto, el segundo es bajo y viceversa, como se muestra a continuación. Algunos circuitos se encienden con la primera señal de sincronización y otros con la segunda. El esquema de funcionamiento del 8086 implica que no hay superposición entre las dos fases de las señales de sincronización y su asimetría; hay una brecha entre los momentos en que una señal de sincronización se vuelve baja y la segunda aumenta.

Un controlador de reloj de dos fases consta de dos señales de reloj de polaridad opuesta

Aunque casi todas las computadoras usan señales de reloj para la sincronización, la máquinaLa arquitectura IAS (popular en la década de 1950) era asincrónica y funcionaba sin señales de reloj. En cambio, cada circuito, cuando termina, envía un pulso al siguiente, lo que activa el siguiente paso. Muchas de las primeras computadoras de la década de 1950 se basaban en esta arquitectura, incluidas CYCLONE, ILLIAC, JOHNNIAC, MANIAC, SEAC e IBM 701. La investigación sobre las posibilidades de la computación asincrónica continúa , pero los sistemas síncronos definitivamente dominan.

Los procesadores, entre otras cosas, utilizan señales de reloj para evitar retroalimentación no deseada en los circuitos. Por ejemplo, considere un contador de software cuya cadena incrementa su valor y lo retroalimenta al contador. No desea que el nuevo valor siga aumentando.

Un método consiste en utilizar disparadores que actualizan el valor cuando la señal pasa de menor a mayor. Luego, el contador se actualizará la única vez que se requiere. Sin embargo, con una señal de sincronización de dos fases, el circuito se puede hacer en pestillos sensibles al nivel, cuyo diseño es mucho más simple que el de los disparadores sensibles a los cambios de señal. Cuando la primera señal de sincronización es alta, la primera mitad del renglón recibe un valor de entrada y realiza cálculos lógicos. Cuando la segunda señal de sincronización es alta, la segunda parte de la cadena recibe el resultado de la primera mitad y realiza todos los cálculos necesarios, y la primera parte se bloquea. El punto es que solo la mitad de la cadena se puede actualizar a la vez, lo que evita comentarios no deseados.

El 8086 tiene requisitos estrictos de reloj de entrada, que deben ser altos durante un tercio del tiempo. Normalmente, el 8086 fue generado por el chip 8284 y un cristal de cuarzo. El chip dividió la señal de reloj entrante por 3 para proporcionar el ciclo de trabajo de reloj del 33% requerido por el 8086.

En los procesadores modernos, el diseño de la señal del reloj es muy complejo porque la señal debe viajar a todas las partes del chip simultáneamente. Los procesadores modernos utilizan una jerarquía de rutas de reloj, equilibran los tiempos de viaje a lo largo de cada ruta y, a menudo, proporcionan almacenamiento en búfer por separado para cada ruta. A modo de comparación, el diseño de la señal de reloj del 8086 es sencillo, ya que su frecuencia de reloj de 5-10 MHz es varios órdenes de magnitud más baja que la de los procesadores modernos. A estas frecuencias relativamente bajas, la longitud de la ruta realmente no importa, por lo que los pulsos de reloj del 8086 pueden seguir rutas sinuosas.

Dado que el 8086 usaba lógica dinámica, también tenía una velocidad de reloj mínima de 2 MHz. Si la frecuencia es menor, existe el riesgo de fugas de carga antes de que se renueve la carga, lo que puede provocar fallas. La frecuencia mínima de reloj era inconveniente desde el punto de vista de la depuración, ya que era imposible ralentizar o detener la señal del reloj.

Rutas de sincronización en el 8086. Verde es la primera sincronización y rojo es la segunda, con fase opuesta

El diagrama de arriba muestra las rutas de reloj del 8086. La fase 1 es verde y la fase 2 es roja. En la parte inferior del chip, los circuitos del controlador del reloj aparecen como puntos grandes. A partir de ahí, las señales de sincronización se ramifican por todo el chip. En su mayor parte, las dos fases del reloj funcionan en paralelo, a diferencia de la energía y la tierra con sus ramas opuestas.

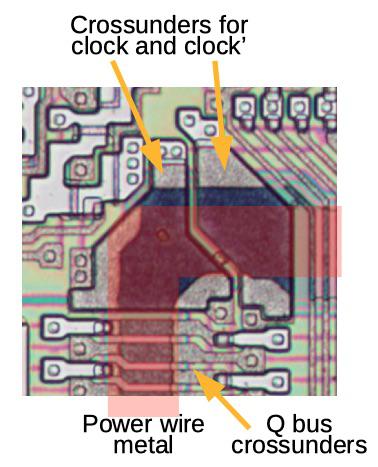

Dado que las señales de reloj llegan a todas las partes del chip, requieren mucha más corriente que las señales convencionales y, por lo tanto, en su mayoría se enrutan a la capa de metal. Cuando las señales de sincronización necesitan cruzar las pistas de potencia, pasan por debajo de ellas, como se muestra a continuación. Tenga en cuenta que las soluciones alternativas de sincronización tienen una forma irregular: son mucho más grandes que las soluciones alternativas para otras señales, como el bus Q.

Las rutas de derivación de la fuente de alimentación son bastante grandes. El bus Q (que transmite comandos desde la cola de comandos al decodificador) tiene mucho menos.

Para proporcionar señales de sincronización de alta corriente, su circuito modelador se basa en grandes transistores. La foto de abajo compara uno de estos transistores con un transistor lógico típico. Los transistores del controlador son aproximadamente 300 veces más grandes, por lo que es capaz de entregar aproximadamente 300 veces la corriente. El transistor se compone de 10 transistores colocados en paralelo - 10 líneas verticales de polisilicio forman 10 puertas. Cada señal de sincronización es generada por un par de grandes transistores, uno de los cuales la eleva y el otro hacia abajo.

Transistor grande en el controlador de reloj en comparación con el transistor lógico adyacente

La foto de abajo muestra el esquema del generador de pulsos de sincronización. El circuito divide la señal del reloj externo en dos fases, asegura que no se superpongan y las amplifica. El cuadrado rosa de la izquierda es una plataforma para un controlador de reloj externo. La señal viaja a través de una serie de transistores que terminan en los grandes transistores del controlador en el lado derecho. Los conductores marrones son polisilicio que forman las puertas. Muchos transistores tienen puertas en zig-zag, por lo que un transistor grande cabe en un espacio pequeño.

Circuito de controlador de reloj en chip. Se ha eliminado la capa de metal. Se ven grandes transistores. Pin de entrada de sincronización externa - cuadrado rosa a la izquierda.

A continuación se muestra un diagrama esquemático ligeramente simplificado del generador de reloj. Los triángulos son controladores de alta corriente hechos de dos o tres transistores. La entrada inversora (círculo) reduce la salida. En el lado izquierdo del pin de sincronización de entrada, hay una pequeña resistencia y un diodo que lo protege (al igual que los otros pines de entrada). La señal de sincronización luego se divide en fase invertida (arriba) y fase invertida (abajo).

Diagrama esquemático simplificado del generador de reloj 8086

Los circuitos adicionales evitan que las señales de sincronización se superpongan: cuando una señal es alta, esto, a través de la entrada invertida, hace que la segunda señal sea baja. Para entender cómo funciona esto, comencemos con el momento en que la señal en el pin clk in es alta. Las señales clk in y clock son altas, mientras que ^ clk in ^ y ^ clock ^ son bajas. Ahora, digamos que la entrada para clk in baja, lo que hace que la señal clk in baje y ^ clk in ^ suba. Sin embargo, la salida de ^ clock ^ no puede subir hasta que el reloj baje. Después de eso, la señal ^ clk in ^ pasará por los controladores inferiores, tirando ^ clock ^ hacia arriba después de dos retrasos en la puerta. El caso es que el reloj y el ^ reloj ^ no cambian al mismo tiempo. Después de que uno baja, hay un retraso antes de que el otro suba.Como resultado, obtenemos señales de sincronización que no se superponen.

Esta es una descripción bastante aproximada; en particular, no estoy seguro de qué sucede cuando un transistor sube una señal y otro baja la misma señal. La simulación exacta del proceso dependerá de los tamaños relativos de los dos transistores.

Conclusión

El 8086 usa una distribución de energía interesante, pero los procesadores modernos operan en un nivel completamente diferente. Si el 8086 necesitaba 350 mA, entonces un procesador moderno podría necesitar más de 100 A. El 8086 usaba 3 de sus 40 patas para alimentación y tierra. Los procesadores Intel Core i5 modernos tienen 128 pines de alimentación y 377 pines de tierra (de un total de 1151 pines). Si bien las numerosas capas de metal en los chips modernos resuelven los problemas de cableado del 8086, introducen nuevas complicaciones como dividir el chip en secciones de potencia, lo que le permite apagar las secciones no utilizadas.

En los procesadores modernos con sus velocidades de varios gigahercios, el cableado de las señales de sincronización es mucho más complicado, porque un milímetro adicional de pista puede afectar negativamente la señal de sincronización. Para resolver estos problemas, los procesadores modernos usan cosas como árboles H o redes de distribución de reloj, en lugar de solo pistas ramificadas como el 8086. Mientras que el 8086 tenía un circuito generador de reloj de dos fases simple, los procesadores modernos a menudo usan bucle de bloqueo de fase para sintetizar la señal del reloj. y muchos circuitos dispersos por todo el chip que proporcionan y controlan señales de reloj. Pero aunque el 8086 es mucho más simple que los procesadores modernos, contiene muchos ejemplos de circuitos interesantes.