Ya he hablado de los recién casados Vladislav y Elena Sharshin, quienes, junto con su colega Andrey Papushin, llevaron a Intel a California para la victoria de plata en la competencia InnovateFPGA. Su entrevista es en el laboratorio "Digital Synthesis" publicado recientemente . Vamos a utilizar este labnik en un seminario para escolares y estudiantes de primer año, que tendrá lugar del 15 al 17 de septiembre en la exposición ChipEXPO en Skolkovo . Si va a repetir (o superar) el logro de Sharshins y Papushin, o simplemente convertirse en un diseñador de FPGA o ASIC sin salir de Santa Clara, participar en un seminario, o incluso simplemente mirar las instrucciones iniciales en esta publicación, lo ayudará a comenzar.

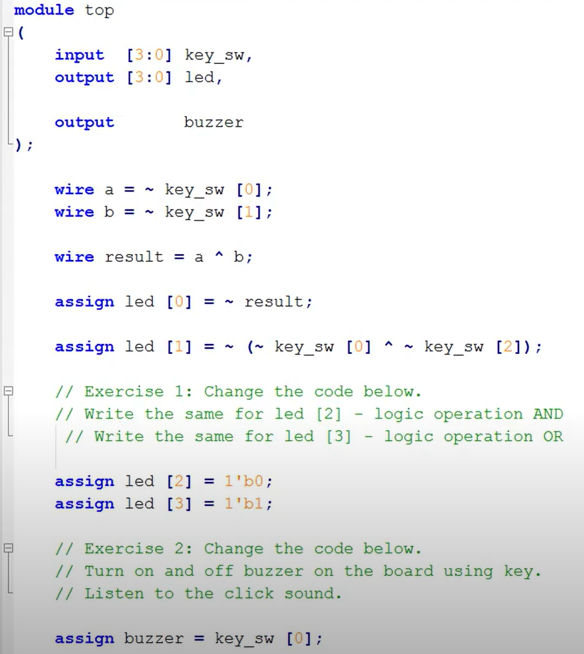

Muchos de los inscritos para el seminario ya han recibido tableros FPGA (son distribuidos por el departamento educativo de RUSNANO) para aprobar el prerrequisito teórico . Ahora sería muy deseable que los participantes del seminario instalaran Intel FPGA Quartus por adelantado (o, si a alguien no le gusta Intel / Altera, entonces Xilinx Vivado), y ejecutaran al menos una prueba primitiva en él. Ni siquiera un LED parpadeante, sino en general una puerta XOR. Si todo el mundo hace esto con anticipación, entonces en el seminario discutiremos problemas no triviales como "No tengo un controlador para USB Blaster", sino algo más interesante, por ejemplo, lo que se pide para una entrevista para el puesto de RTL Logic Designer en NVidia, AMD, Apple y otras empresas.

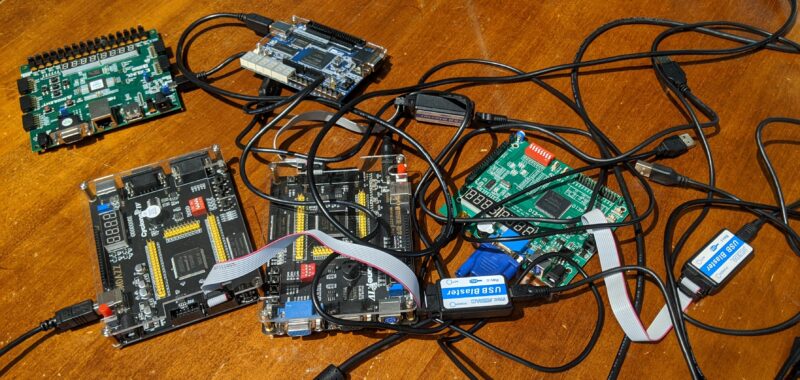

Entonces, en primer lugar, el seminario tiene una organización en github . Puede clonar el repositorio ce2020labs desde aquí y usar los archivos en el directorio anterior para probar su placa, instalar Quartus o Vivado, controladores y solucionar problemas con el programador. El directorio contiene archivos para siete placas: cinco placas con Intel FPGA (dos variantes OMDAZZ / rzrd, dos variantes ZEOWAA y Terasic DE10-Lite) y dos placas con Xilinx (Basys3 y Nexys4).

Si no desea utilizar GitHub, simplemente puede descargar el zip desde aquí . Todos estos archivos funcionarán con las versiones de Windows y Linux de Quartus y Vivado.

Para instalar Quartus, puede ver un video detallado de Sergey Ivants, Decano de la Facultad de Tecnologías Electrónicas y de Información de la Universidad Tecnológica Nacional de Chernihiv:

Video:

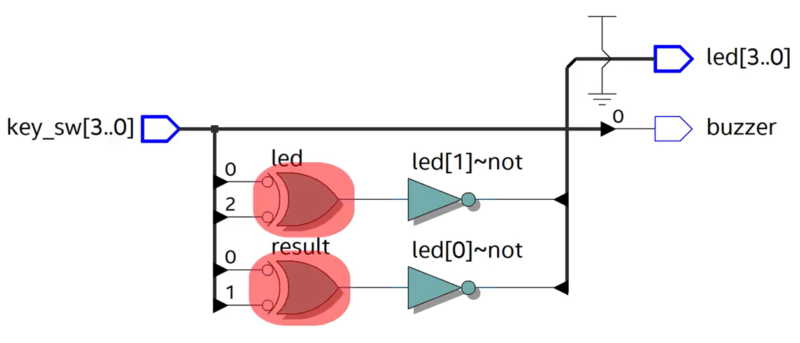

Y un video sobre la síntesis del ejemplo más simple de la descripción en el lenguaje Verilog:

Con una descripción detallada de qué es qué:

El único problema es que este video no cubre muy bien el uso del programador (y problemas con sus controladores). Por lo tanto, puede resultarle útil ver otro video, también de Sergey, donde describe el uso de USB Blaster después del editor de esquemas. Aquí hay que decir que la entrada esquemática dejó de ser utilizada por los diseñadores de microelectrónica digital a principios de la década de 1990 (todos cambiaron al diseño utilizando los lenguajes de descripción de hardware Verilog y VHDL), pero Sergei, sin embargo, decidió mostrar esto puramente para que un estudiante que comenzara a involucrarse en el diseño digital lo hiciera intuitivamente de inmediato. Me di cuenta de que estamos diseñando circuitos y no escribiendo programas, aunque el código en verlog es similar al código en un lenguaje de programación.

Aquí hay un video de la entrada esquemática, al final del cual se describe el uso del programador:

Antes, durante y después del seminario en ChipEXPO en Skolkovo, continuaremos cargando varios materiales, pero para verlo todo (incluida, por ejemplo, una mini conferencia sobre cómo se organizan los equipos de desarrollo de chips en Silicon Valley), es mejor registrarse.