El 8086 tiene más de 80 pestillos. Algunos de ellos almacenan los valores de los pines AD (dirección / datos) o pines de control. Otros almacenan la dirección actual del microcódigo y el microcódigo, así como la dirección de retorno de la rutina del microcódigo. El tercero almacena los bits del registro de comando de origen y salida, y la operación ALU del comando. Muchos almacenan los estados del estado interno, que todavía entiendo.

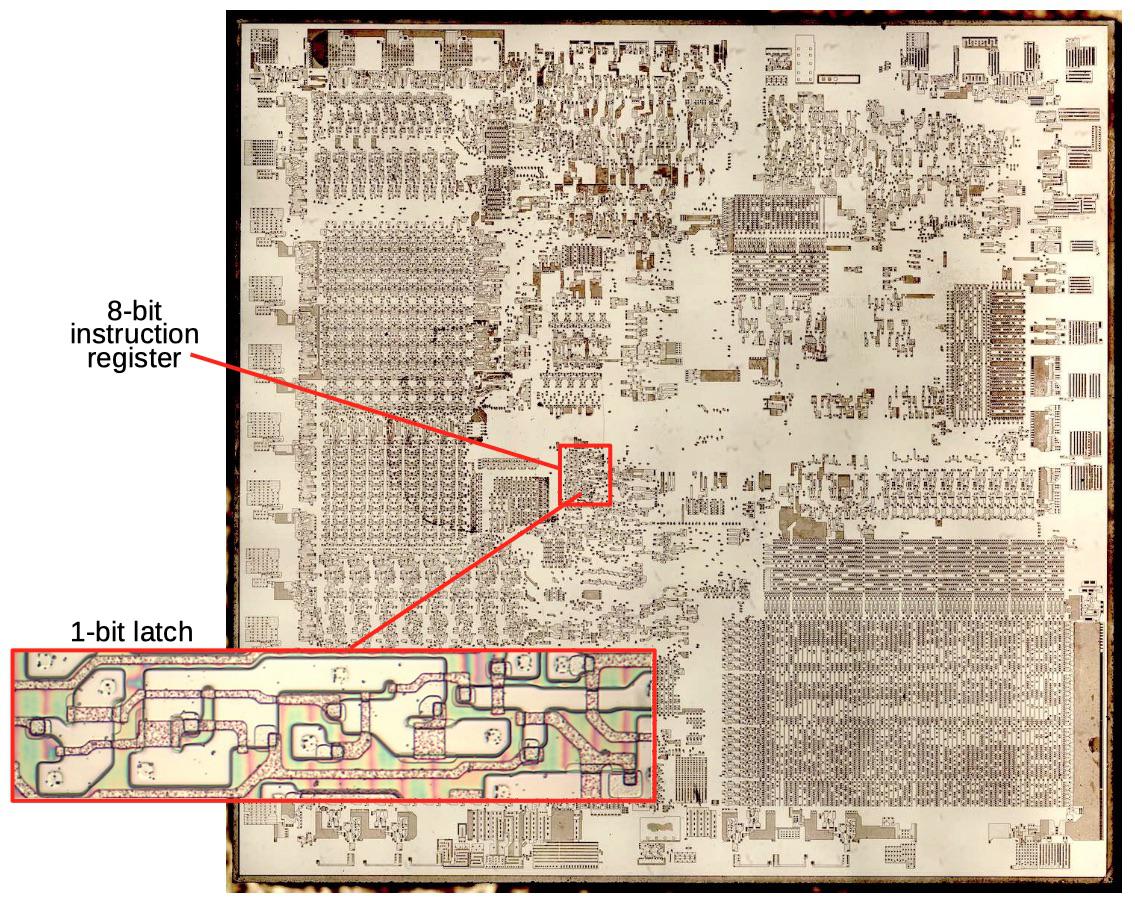

Crystal 86 que muestra el registro de instrucciones de 8 bits

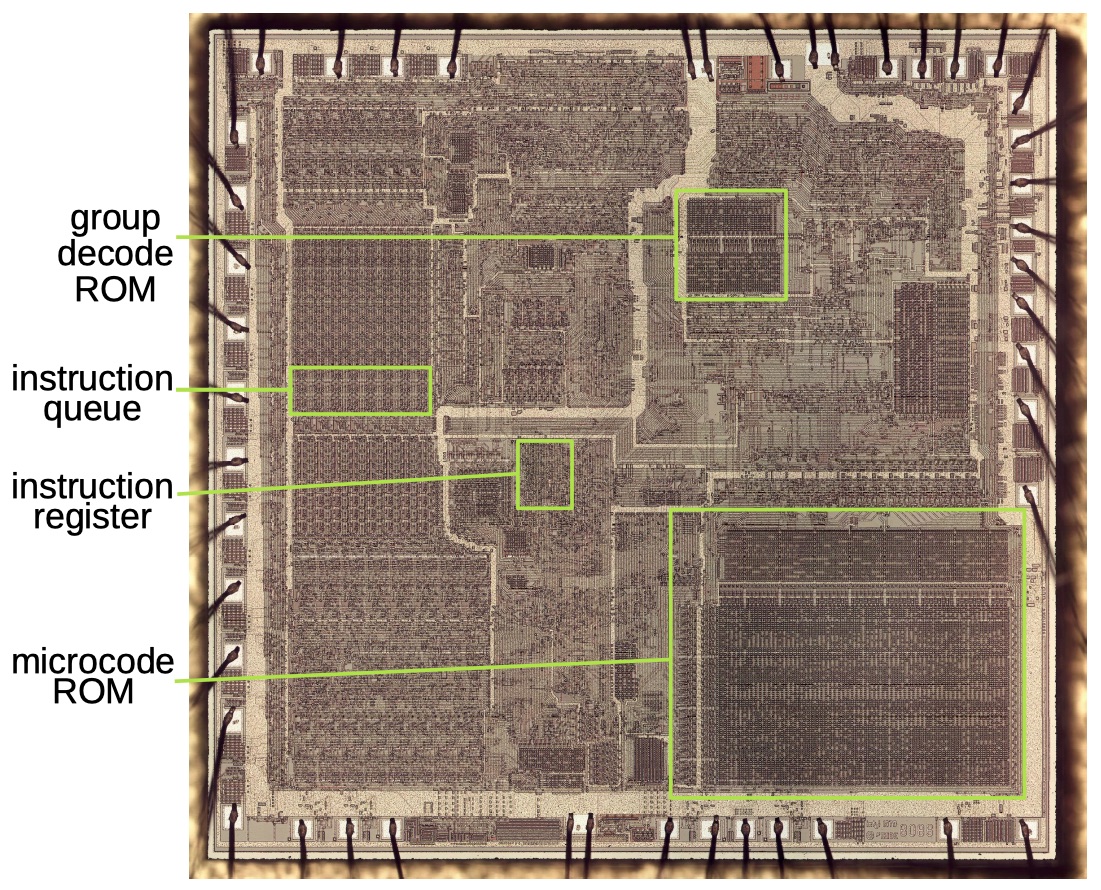

La foto de arriba muestra la matriz de silicio 8086 bajo un microscopio. Quité las capas de metal y polisilicio para que pueda ver los transistores; hay alrededor de 29,000 en total. El área asignada contiene un búfer de comando de 8 bits, que consta de ocho pestillos. Este procesador de 1978 todavía era lo suficientemente simple como para que un solo registro de 8 bits ocupara un área relativamente grande. El aumento muestra silicio y transistores que forman un solo pestillo.

Cómo funciona un pestillo dinámico

El pestillo es uno de los elementos más importantes del 8086, ya que los pestillos realizan un seguimiento de lo que está haciendo el procesador. Los pestillos se pueden realizar de diferentes formas; el 8086 utiliza un circuito compacto conocido como pestillo dinámico. El pestillo dinámico se basa en el funcionamiento de un generador de reloj de dos fases, que a menudo se usaba para controlar microprocesadores de esa época. El reloj de dos fases genera dos señales de reloj que están activas a su vez. En la primera fase, el reloj principal está alto y el reloj que lo acompaña está bajo. Luego cambian de lugar. El ciclo se repite a una frecuencia de reloj, por ejemplo, 5 MHz.

Muchos microprocesadores utilizan puertas NAND para formar flip-flops RS. Un flip-flop RS generalmente ocupa más espacio que un pestillo dinámico, especialmente si se le agregan circuitos adicionales para mantener la frecuencia del reloj. Los disparadores D (disparadores de retardo) también son populares, pero se vuelven aún más complejos y usan seis puertas. En muchos casos, un transistor de paso es suficiente; puede almacenar un valor para un ciclo de reloj, pero no proporciona almacenamiento a largo plazo.

Siempre se elige la velocidad de reloj más alta posible para los procesadores. El primer 8086 funcionó a hasta 5 MHz, y luego el 8086-1 admitió hasta 10 MHz. Sin embargo, debido al uso de lógica dinámica, el 8086 también tiene una frecuencia de reloj mínima: 2 MHz. Si el generador de reloj funciona más lento, existe el riesgo de que se produzcan fugas de carga de los conductores antes de que los circuitos accedan a él, lo que provocaría errores.

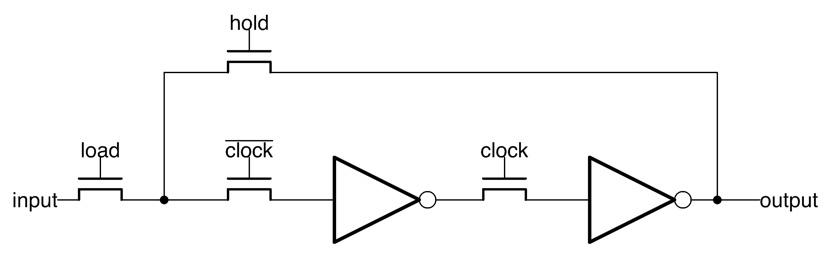

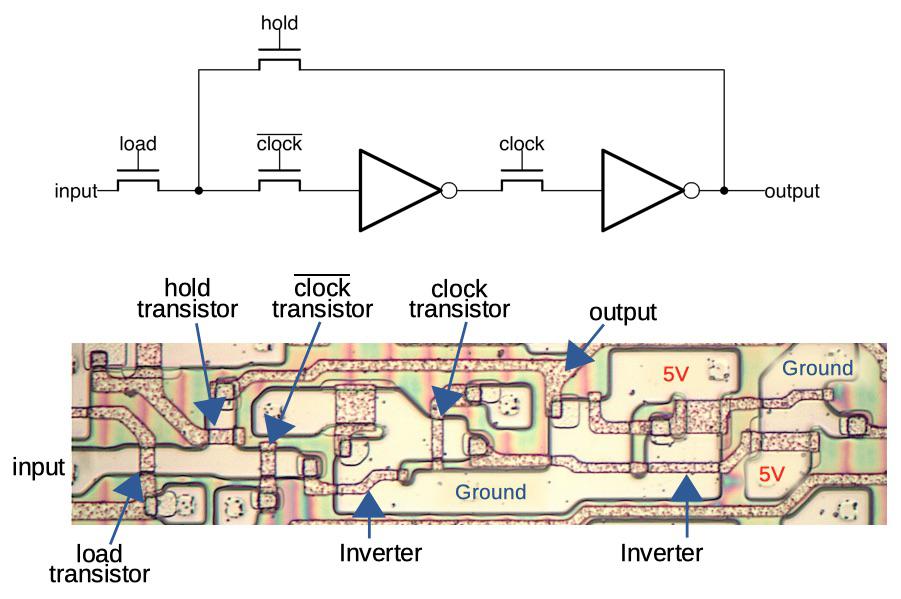

El pestillo del procesador 8086 consta de cuatro transistores de paso y dos inversores. El pestillo funciona con señales de reloj intermitentes.

El diagrama de arriba muestra un pestillo típico 8086. Consta de dos inversores y varios transistores de paso. Para nuestros propósitos, el transistor de paso se puede considerar un interruptor: si 1 llega a la puerta, el transistor transmite la señal más. Si llega 0, el transistor bloquea la señal. El transistor de paso está controlado por varias señales: carga, que carga un poco en el pestillo; mantener (mantener), manteniendo el valor de bit existente; el reloj de la primera fase y el reloj de la segunda, invertidos.

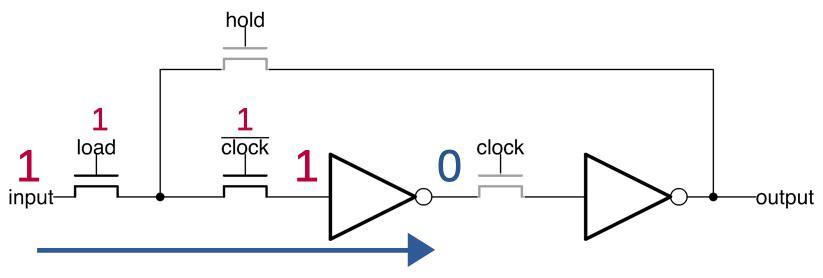

El siguiente diagrama muestra cómo se carga un valor (en este caso, 1) en el pestillo. La señal de carga aumenta, permitiendo que la señal de entrada (1) pase a través del transistor. Dado que la señal del relojalto, la señal pasa a través del segundo transistor al inversor, que emite 0. En este momento, el tercer transistor (reloj) bloquea la señal.

La señal de entrada se carga en el pestillo cuando la señal de carga es alta

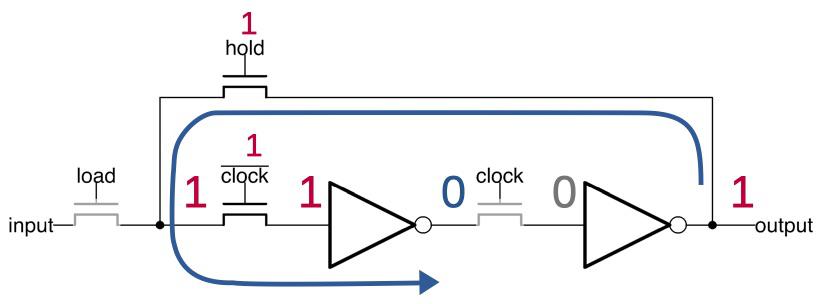

En la siguiente fase del reloj, la señal del reloj sube, lo que hace que la señal 0 llegue al segundo inversor, que emite 1. Dado que la señal de retención es alta, la señal regresa pero es bloqueada por el transistor del reloj.... Lo que hace que este circuito sea dinámico es que actualmente no se envían señales de entrada al primer inversor. Su entrada sigue siendo 1 (mostrada en gris) debido a la capacitancia del circuito. Algún día esta carga se filtrará, el valor se perderá, pero antes de ese momento se producirá una nueva conmutación del generador de pulsos de reloj.

Cuando la señal del reloj sube, el valor pasa a través del segundo inversor. La entrada al primer inversor (gris) está respaldada por la capacitancia del circuito.

Después de cambiar el estado del generador de reloj, la entrada al segundo inversor proporcionará la capacidad del circuito (ver más abajo). La señal vuelve, recargando y actualizando la entrada al primer inversor. En relojes posteriores, el pestillo alternará entre este y el patrón anterior, manteniendo el valor almacenado y manteniendo estable la salida.

La clave para el funcionamiento del pestillo es la presencia de dos inversores, que mantienen estable la señal de salida. Un número impar de inversores causaría oscilación: esta función es utilizada por la bomba de carga 8086. Además, un par de inversores utiliza un conjunto de registros 8086 para almacenar bits. Sin embargo, en un conjunto de registros, los dos inversores están conectados directamente, sin los transistores de paso controlados por reloj, lo que resulta en un sistema de almacenamiento más compacto pero difícil de administrar.

Cuando la señal del reloj es alta, el valor pasa por el primer inversor.

Implementación en silicio

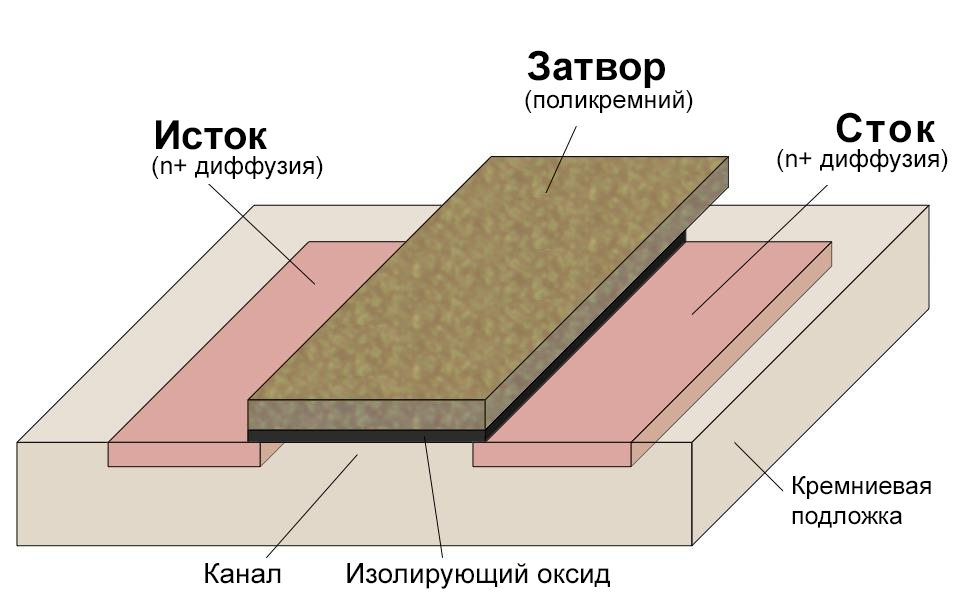

El 8086 y otros procesadores de esa época se basaban en transistores N-MOS . Estaban hechos de un sustrato de silicio, al que se añadían impurezas de arsénico o boro durante el proceso de dopaje , que formaban los transistores. Encima del silicio había polisilicio, que creaba las puertas de los transistores y los conductores que conectaban todos los componentes. Otra capa, de metal, proporcionó conexiones conductoras adicionales. Los procesadores modernos, en comparación, utilizan tecnología CMOS , una combinación de tecnologías N-MOS y P-MOS, y tienen más de una capa conductora metálica.

Cómo se implementa un transistor N-MOS ( estructura MOS ) en un IC

El diagrama de arriba muestra la estructura del transistor. Se puede pensar en un transistor como un interruptor que permite que la corriente fluya de una sección (fuente) a otra (drenaje). El transistor es impulsado por una puerta hecha de un tipo especial de silicio: polisilicio. La aplicación de un voltaje a la puerta permite que la corriente fluya entre la fuente y el drenaje, mientras que tirar de la puerta a 0 V bloquea la corriente. La puerta está separada del silicio por una capa de óxido aislante; debido a esto, la puerta funciona como un condensador, como se puede ver en el ejemplo de un pestillo dinámico.

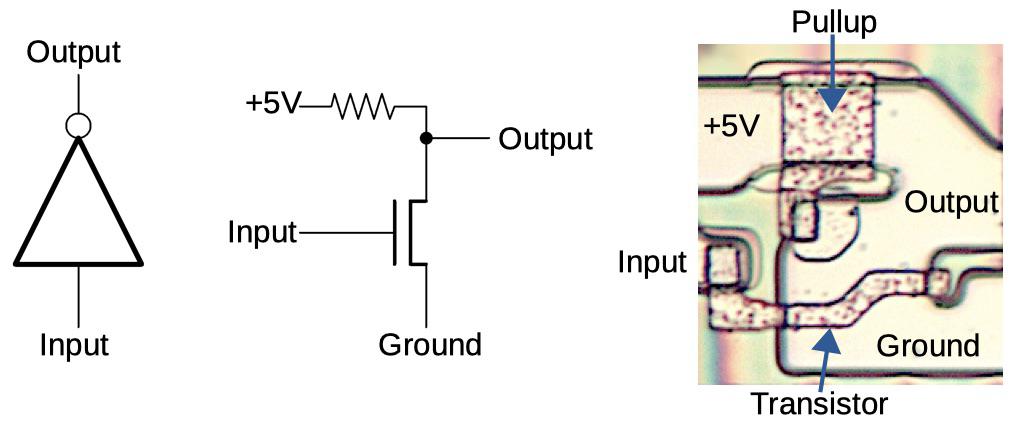

El inversor (abajo) está compuesto por un transistor N-MOS y una resistencia. Cuando la señal es baja, el transistor está apagado, por lo que la resistencia pull-up eleva la señal de salida. Cuando la señal es alta, el transistor se enciende, conectando la salida a tierra y bajando la salida. Por tanto, el circuito invierte la señal de entrada.

La resistencia pull-up en la puerta N-MOS se implementa utilizando un tipo especial de transistor. Un transistor en modo de agotamiento funciona como una resistencia, pero ocupa menos espacio y es más eficiente.

El diagrama muestra cómo está hecho un inversor a partir de un transistor y una resistencia. La foto muestra cómo se implementa el circuito en el chip. La capa de metal se ha eliminado para revelar polisilicio y silicio.

La foto de la derecha muestra cómo el 8086 implementa físicamente un inversor. Las áreas amarillentas son de silicio conductor con impurezas y las áreas con manchas son de polisilicio en la parte superior. El transistor se fabrica donde el polisilicio cruza el silicio dopado. El polisilicio forma la puerta del transistor y las secciones de silicio en ambos lados proporcionan la fuente y el drenaje del transistor. Un gran rectángulo de polisilicio forma una resistencia pull-up entre + 5V y la salida. Puede comparar la estructura de estas estructuras físicas con un diagrama.

El siguiente diagrama muestra la implementación del pestillo en el chip. Se marcan un transistor de paso y dos inversores; el primer inversor se describe arriba. Los conductores de polisilicio conectan los componentes entre sí. Se proporcionaron conexiones adicionales mediante una capa de metal (eliminada para la foto). La forma compleja de los transistores permite el uso más eficiente del espacio.

Foto microscópica del pestillo en el procesador 8086. Se ha eliminado la capa metálica con los conductores, pero sus trazas son visibles en forma de líneas verticales rojizas. Foto girada 180 ° para adaptarse al diseño.

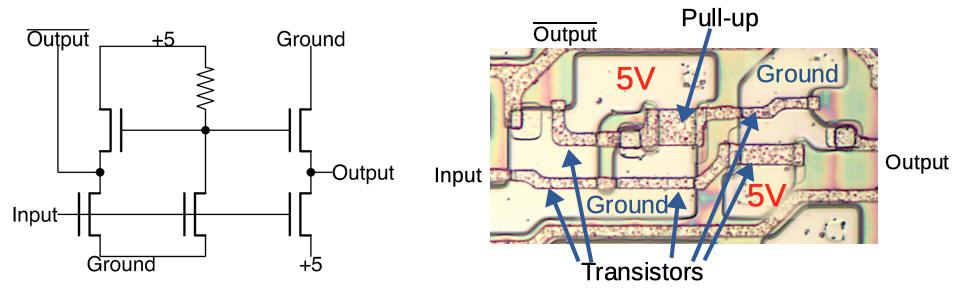

El pestillo utiliza búferes de salida no marcados en el diagrama para proporcionar señales de alta corriente para la salida y la salida invertida. Estos búferes tienen un nombre divertido, "superbuffers", porque entregan una corriente mucho más alta que un inversor N-MOS típico. El problema con un inversor N-MOS es que funciona lentamente cuando conduce algún circuito de alta capacidad. Dado que el superbuffer entrega más corriente, cambia la señal mucho más rápido. Lo logra reemplazando la resistencia pull-up con un transistor de corriente más alta. La desventaja es que el transistor pull-up requiere un inversor para funcionar, por lo que el circuito del superbuffer es más complicado. Por lo tanto, el superbuffer se usa solo cuando es necesario, generalmente cuando se envía una señal a muchas puertas o cuando se conduce un autobús largo.

Implementación del superbuffer con pestillo 8086. Observe que las conexiones de +5 V y de tierra se mueven a los transistores más a la derecha.

El diagrama anterior muestra un esquema del superbuffer de pestillo 8086. A diferencia de un superbuffer convencional, este tiene un superbuffer inversor y otro no inversor. Para comprender el circuito, tenga en cuenta que la resistencia central y el transistor forman un inversor. La salida del inversor está conectada a los transistores superiores y la entrada no invertida está conectada a los transistores inferiores. Luego, si la entrada es 1, los transistores inferiores se encienden, y si la entrada es 0, entonces gracias al inversor, los transistores superiores se encienden. Luego, si la entrada es 1, los transistores inferiores subirán la salida y bajarán la salida correspondiente . Si la entrada es 0, los transistores superiores bajarán la salida y la salida correspondiente- arriba.

El problema con el inversor N-MOS es que la resistencia pull-up tiene una corriente limitada. Cuando la salida es 0, el transistor en el inversor rápidamente y con una corriente relativamente alta reduce la salida. Sin embargo, si la salida es 1, la salida es levantada por una resistencia pull-up mucho más débil.

Un superbuffer es similar a un inversor CMOS en que tiene un transistor pull-up y un transistor pull-down. La diferencia es que CMOS usa transistores P-MOS y N-MOS, mientras que P-MOS usa una entrada de puerta invertida. Por el contrario, un superbuffer N-MOS requiere un inversor separado. En otras palabras, un inversor CMOS usa dos transistores, y un superbuffer es mucho menos eficiente porque requiere cuatro transistores.

El superbuffer utiliza un transistor de modo de mejora para subir y un transistor de modo de mejora para bajar. El voltaje de umbral de un transistor con su propio canal está por debajo de cero, lo que permite que su salida se eleve a 5 V y no se apague a un voltaje más bajo. Cuando la salida es baja, el transistor de autocanalización seguirá encendido y actuará como un pull-up normal en un inversor convencional, por lo que una cierta cantidad de corriente fluirá a través de él. Puede leer más sobre el superbuffer aquí .

Registro de comando

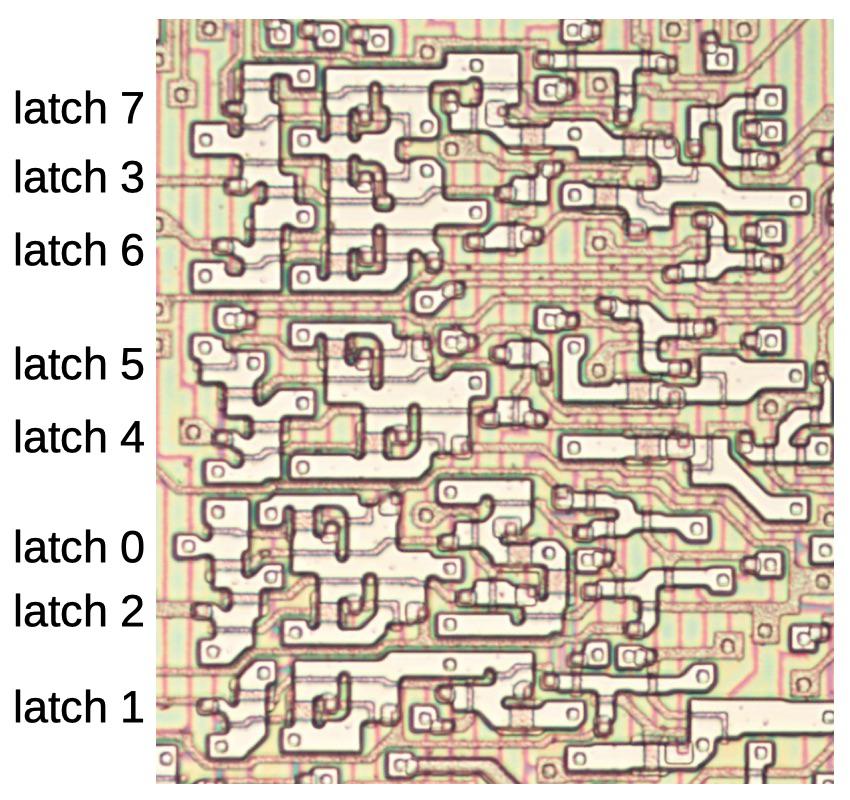

Como la mayoría de los procesadores, el 8086 tiene un registro de instrucciones donde se almacena la instrucción en ejecución. En el 8086, el registro de comando contiene el primer byte del comando (que puede ser de varios bytes), por lo que se compone de ocho pestillos. Uno pensaría que serían idénticos, sin embargo, cada uno de ellos tiene su propia forma. El diseño del 8086 está altamente optimizado, por lo que la forma de cada pestillo está diseñada para aprovechar al máximo el espacio disponible debido a las limitaciones de los conductores circundantes. En particular, tenga en cuenta que algunos pestillos se conectan entre sí y comparten energía y tierra. Al parecer, por la misma razón, los pestillos no van en fila.

Los 8 pestillos tienen formas ligeramente diferentes, optimizadas para los conductores circundantes. Anteriormente en el artículo, el pestillo n. ° 1 se giró 180 °. Las líneas verticales rojas son rastros de la capa de metal eliminada.

El equipo recorre el 8086 por un camino sinuoso. El procesador utiliza una captación previa que mejora el rendimiento, cargando instrucciones desde la memoria antes de que sean necesarias. Se almacenan en la cola de comandos, una cola de 6 bytes ubicada en medio de un conjunto de registros. En comparación, los procesadores modernos tienen una caché de comandos que puede llegar a ser de varios megabytes.

Cuando se ejecuta un comando, se almacena en el registro de comando, aproximadamente en el centro del chip. Las distancias relativamente grandes explican la necesidad de un superbuffer. El registro de comandos envía el comando a la "ROM de descifrado de grupo". Esta ROM define las características de alto nivel del comando, ya sea de un solo byte, multibyte o es el prefijo del comando. Y esto es solo una pequeña parte del complejo sistema de procesamiento de instrucciones 8086. Otros pestillos almacenan partes de las instrucciones, marcando el uso del registro y las operaciones de ALU, y un circuito separado controla el motor de microcódigo, pero lo describiré por separado.

Crystal 8086, los componentes clave para el procesamiento de comandos están marcados. A lo largo del perímetro, los cables de soldadura conectan el cristal a los contactos externos.

Conclusión

El 8086 hace un uso extensivo de pestillos dinámicos para almacenar estados internos. Son visibles al microscopio y sus circuitos se pueden rastrear y comprender. El cristal 8086 es interesante de analizar porque, a diferencia de los procesadores modernos, sus transistores son lo suficientemente grandes como para ser vistos bajo un microscopio. Era un procesador sofisticado con 29.000 transistores para su época, pero lo suficientemente simple como para rastrear y comprender sus circuitos.