Todas las unidades centrales de procesamiento de cualquier computadora, ya sea una computadora portátil barata o un servidor por millones de dólares, tienen un dispositivo llamado caché. Y con una probabilidad muy alta tiene varios niveles.

Probablemente sea importante, de lo contrario, ¿por qué instalarlo? Pero, ¿qué hace el caché y por qué tiene diferentes niveles? ¿Y qué significa "asociativo de conjuntos de 12 vías"?

¿Qué es la caché?

TL; DR: esta es una memoria pequeña pero muy rápida ubicada muy cerca de los bloques lógicos de la CPU.

Sin embargo, por supuesto, podemos aprender mucho más sobre el caché ...

Comencemos con un sistema de almacenamiento mágico imaginario: es infinitamente rápido, puede manejar un número infinito de transferencias de datos al mismo tiempo y siempre proporciona un almacenamiento confiable y seguro. Por supuesto, nada de eso existe cerca, pero si esto fuera así, la estructura del procesador sería mucho más simple.

Entonces, los procesadores solo necesitarían bloques lógicos para sumar, multiplicar, etc., así como un sistema de control de transmisión de datos, porque nuestro sistema de almacenamiento teórico es capaz de transmitir y recibir instantáneamente todos los números necesarios; ningún bloque lógico tiene que permanecer inactivo mientras se espera que se transfieran los datos.

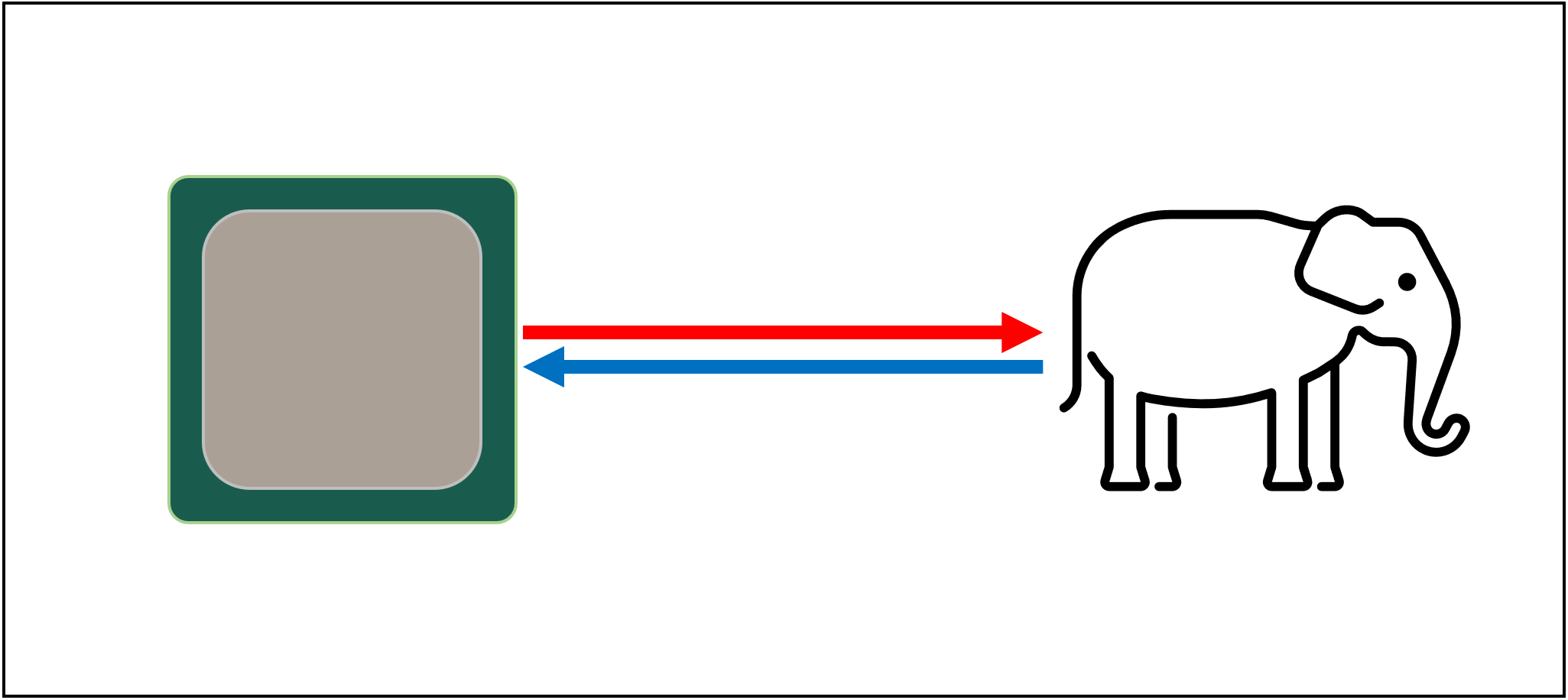

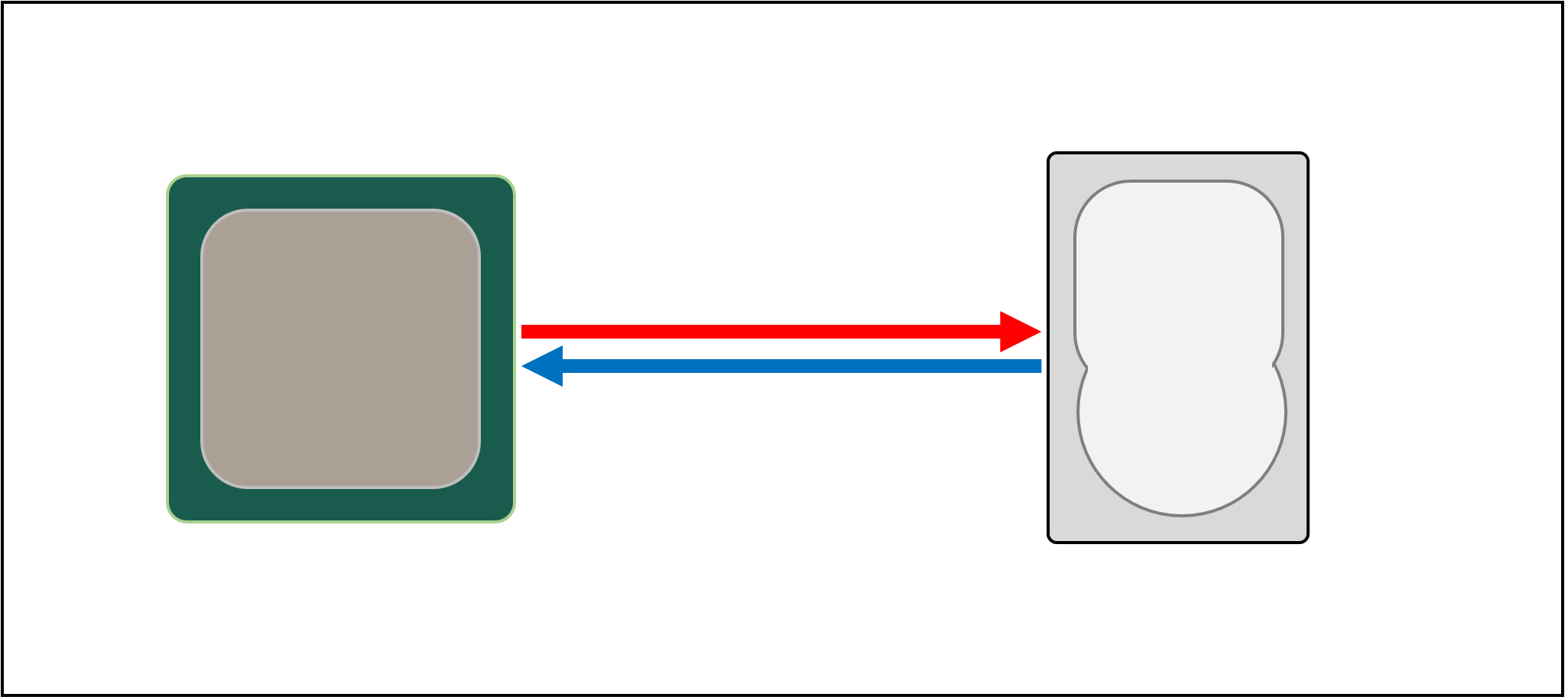

Pero, como sabemos, no existe tal tecnología de almacenamiento mágico. En cambio, tenemos discos duros o unidades de estado sólido, e incluso los mejores de ellos están muy por debajo de las capacidades de procesamiento que requiere un procesador moderno.

El gran T'Fon del almacenamiento

La razón de esto es que los procesadores modernos son increíblemente rápidos: solo necesitan un ciclo de reloj para agregar dos enteros de 64 bits; si el procesador está funcionando a 4 GHz, esto es solo 0.00000000025 segundos, o un cuarto de nanosegundo.

Al mismo tiempo, un disco duro giratorio tarda miles de nanosegundos solo en encontrar datos en los discos, sin mencionar su transferencia, y las unidades de estado sólido tardan decenas o cientos de nanosegundos.

Obviamente, tales unidades no se pueden construir dentroprocesadores, por lo que habrá una separación física entre ellos. Por lo tanto, se agrega tiempo para mover datos, lo que agrava la situación.

Por desgracia, este es el gran A'Tuin del almacenamiento de datos.

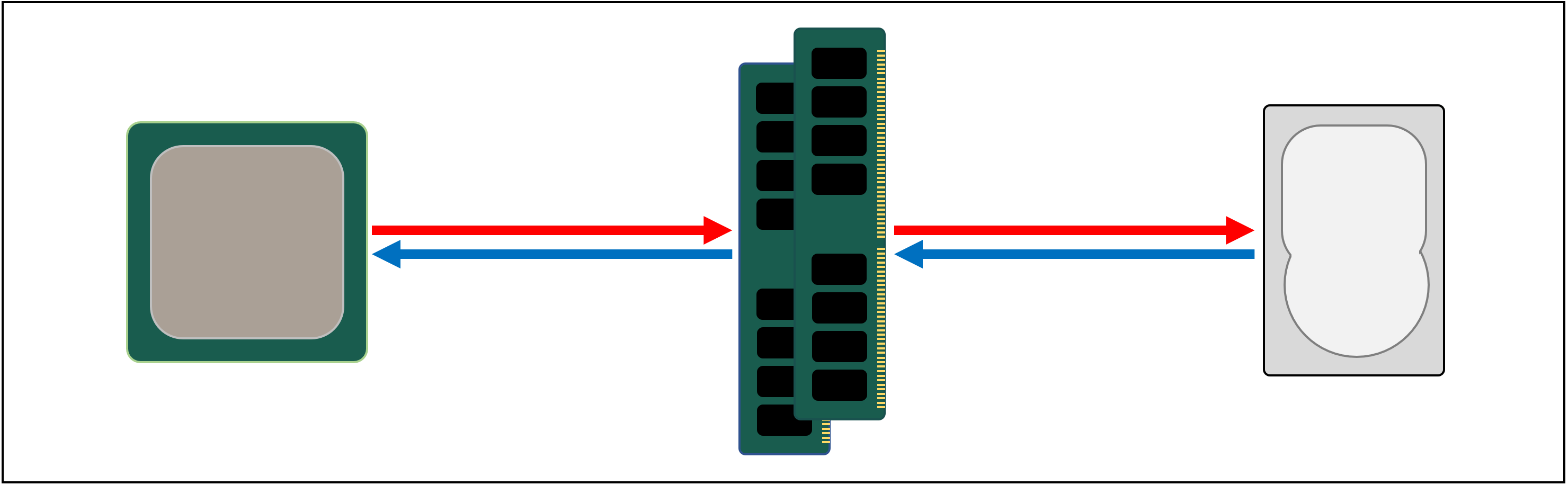

Es por eso que necesitamos otro sistema de almacenamiento ubicado entre el procesador y la unidad principal. Debe ser más rápido que un dispositivo de almacenamiento, capaz de manejar múltiples transferencias de datos simultáneamente y estar mucho más cerca del procesador.

Bueno, ya tenemos un sistema así, y se llama RAM ; está presente en todas las computadoras y realiza exactamente esta tarea.

Casi todos estos almacenamientos son del tipo DRAM ( memoria dinámica de acceso aleatorio) ; son capaces de transferir datos mucho más rápido que cualquier dispositivo de almacenamiento.

Sin embargo, a pesar de su enorme velocidad, DRAM no es capaz de almacenar tales cantidades de datos.

Algunos de los chips de memoria DDR4 más grandes desarrollados por Micron almacenan 32 Gb, o 4 GB de datos; los discos duros más grandes almacenan 4.000 veces más.

Entonces, aunque hemos aumentado la velocidad de nuestra red de datos, necesitaremos sistemas adicionales (hardware y software) para determinar qué datos deben almacenarse en una cantidad limitada de DRAM, listos para ser procesados por el procesador.

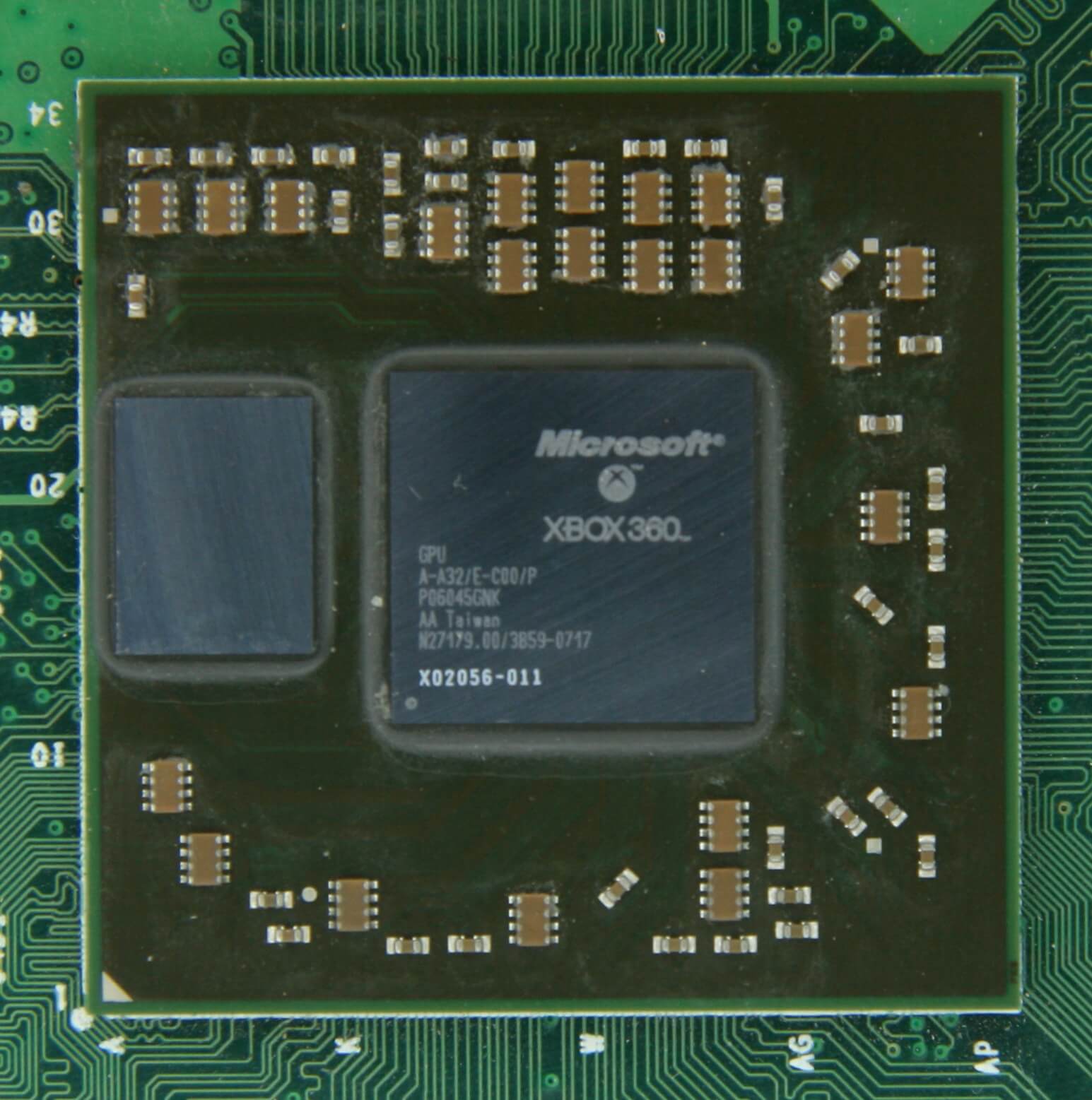

La DRAM se puede fabricar en un paquete de chips (esto se denomina DRAM integrada). Sin embargo, los procesadores son bastante pequeños, por lo que no caben en una gran cantidad de memoria.

DRAM de 10 MB a la izquierda de la GPU Xbox 360. Fuente: CPU Grave Yard

La gran mayoría de DRAM se encuentra muy cerca del procesador, conectada a la placa base y siempre es el componente más cercano al procesador. Sin embargo, esta memoria todavía no es lo suficientemente rápida ... La

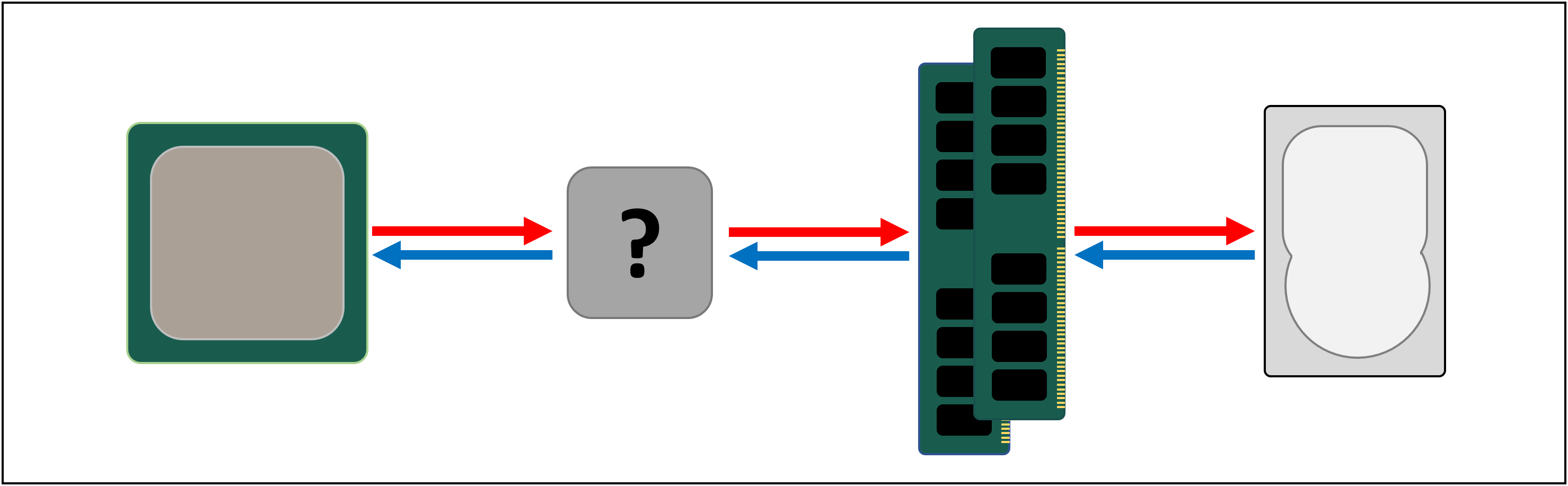

DRAM tarda unos 100 nanosegundos en encontrar datos, pero al menos es capaz de transferir miles de millones de bits por segundo. Parece que necesitamos otra etapa de memoria que se pueda colocar entre la CPU y los bloques de DRAM.

La etapa restante aparece en escena: SRAM ( memoria estática de acceso aleatorio). DRAM usa condensadores microscópicos para almacenar datos en forma de carga eléctrica, mientras que SRAM usa transistores para la misma tarea, que operan a la misma velocidad que los bloques lógicos del procesador (aproximadamente 10 veces más rápido que DRAM).

Por supuesto, SRAM tiene un inconveniente y nuevamente tiene que ver con el espacio.

La memoria de transistores ocupa mucho más espacio que la DRAM: en el mismo tamaño que un chip DDR4 de 4 GB, puede obtener menos de 100 MB de SRAM. Pero dado que se fabrica utilizando el mismo proceso de fabricación que la CPU, SRAM se puede incrustar directamente dentro del procesador, lo más cerca posible de los bloques lógicos.

Con cada paso adicional, aumentamos la velocidad de los datos transferidos a costa del volumen almacenado. Podemos continuar y agregar nuevos pasos, que serán más rápidos, pero más pequeños.

Y así llegamos a una definición más estrictaconceptos de caché: una colección de SRAM ubicada dentro del procesador; maximizan la utilización del procesador al transferir y almacenar datos a velocidades muy altas. ¿Está satisfecho con esta definición? ¡Genial, porque las cosas se complicarán mucho más a partir de ahora!

Efectivo: estacionamiento multinivel

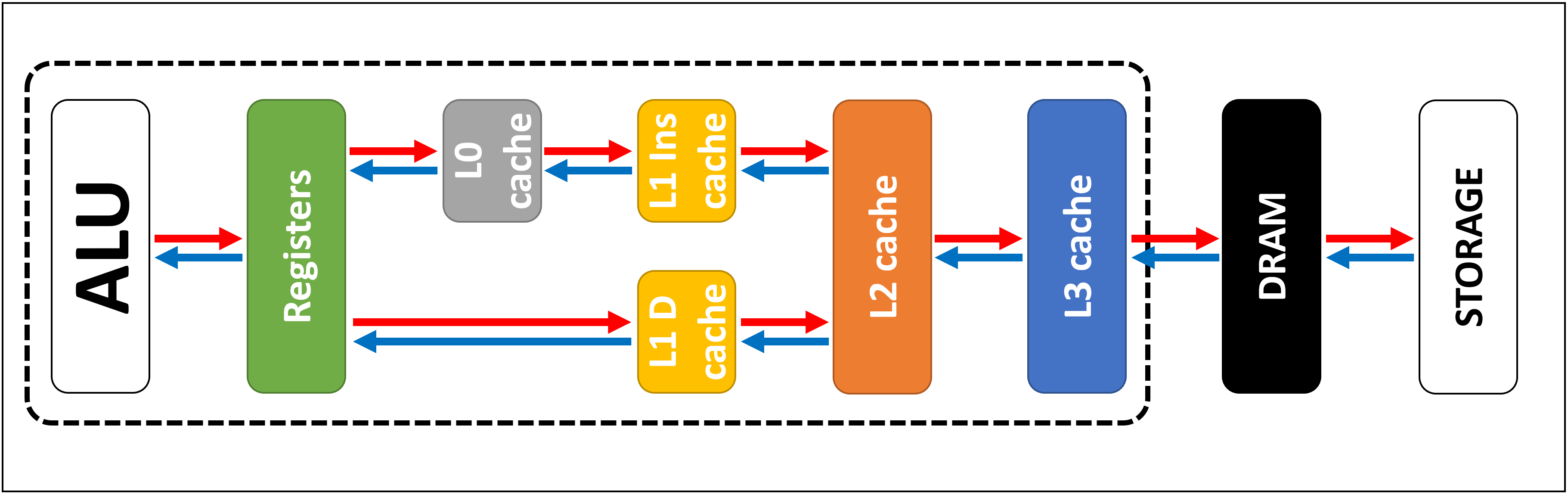

Como dijimos anteriormente, la caché es necesaria porque no tenemos un sistema de almacenamiento mágico que pueda manejar el consumo de datos de los bloques lógicos del procesador. Las CPU y GPU modernas contienen muchas SRAM, organizadas dentro de una jerarquía, una secuencia de cachés con la siguiente estructura:

En la imagen de arriba, el procesador (CPU) se indica con un rectángulo de trazos. A la izquierda están las ALU (unidades lógicas aritméticas); estas son estructuras que realizan operaciones matemáticas. Aunque no es estrictamente un caché, el nivel de memoria más cercano a la ALU son los registros (están ordenados en un archivo de registro ).

Cada uno de ellos almacena un número, por ejemplo, un entero de 64 bits; el valor en sí mismo puede ser un elemento de algunos datos, un código de una instrucción específica o una dirección de memoria de algunos otros datos.

El archivo de registro en los procesadores de escritorio es bastante pequeño, por ejemplo, en cada uno de los núcleos Intel Core i9-9900Khay dos bancos de dichos archivos, y el de enteros contiene solo 180 enteros de 64 bits. Otro archivo de registro para vectores (pequeñas matrices de números) contiene 168 elementos de 256 bits. Es decir, el archivo de registro total para cada núcleo es un poco menos de 7 KB. A modo de comparación, el archivo de registro Nvidia GeForce RTX 2080 Ti para multiprocesadores de transmisión (como las GPU llaman a los análogos del núcleo de la CPU) tiene un tamaño de 256 KB.

Los registros, como el caché, son SRAM, pero su velocidad no excede la velocidad de las ALU a las que sirven; transfieren datos en un ciclo de reloj. Pero no están diseñados para almacenar grandes cantidades de datos (solo un elemento), por lo que siempre hay bloques de memoria más grandes junto a ellos: este es el caché de primer nivel (Nivel 1).

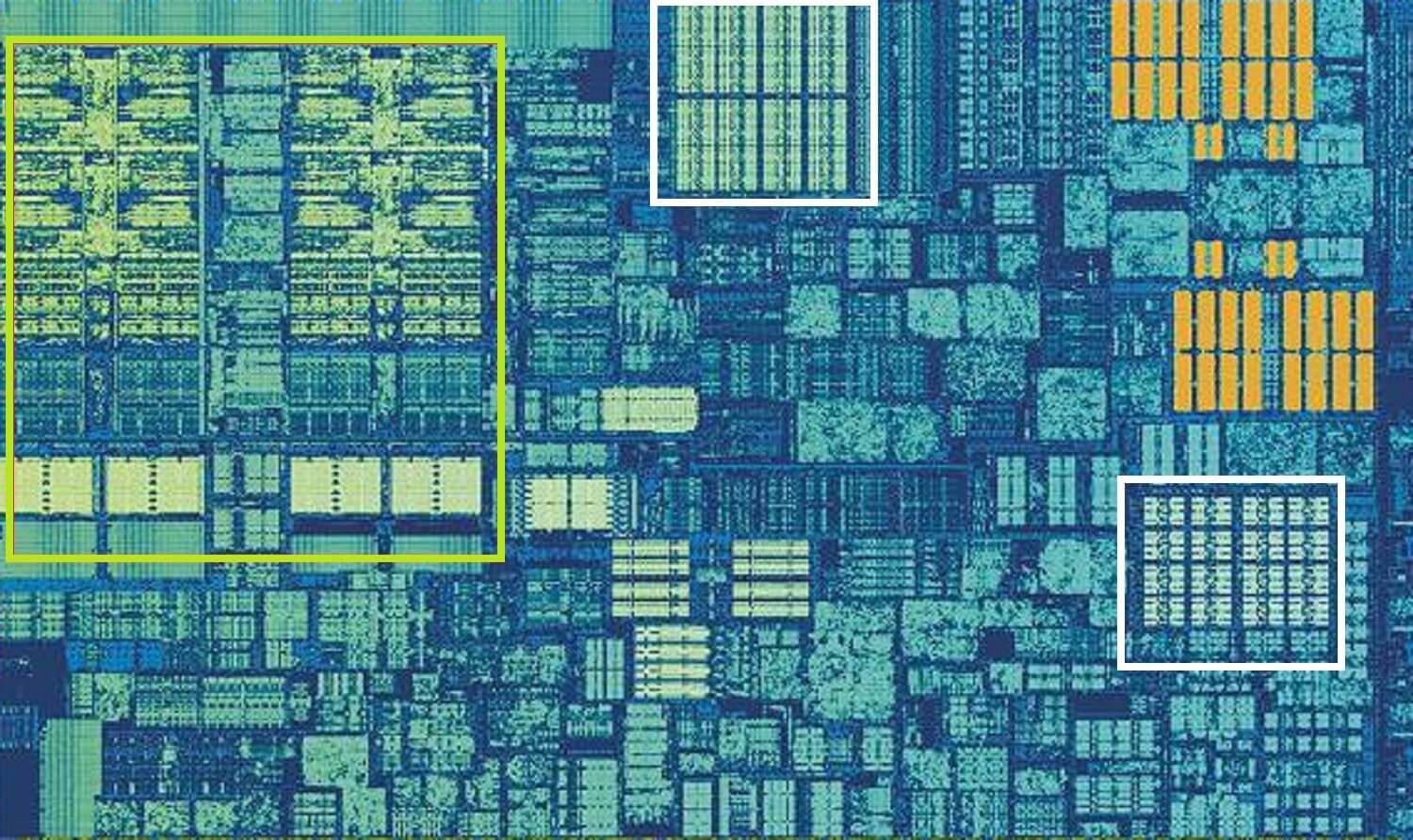

Un núcleo de procesador Intel Skylake. Fuente: Wikichip

La imagen de arriba es una vista ampliada de uno de los núcleos del procesador de escritorio Intel Skylake .

Los archivos de registro y ALU se encuentran a la izquierda y están rodeados por un marco verde. En la parte superior de la foto, la caché de datos de nivel 1 se indica en blanco. No contiene mucha información, solo 32 KB, pero al igual que los registros, se ubica muy cerca de los bloques lógicos y opera a la misma velocidad que estos.

Otro rectángulo blanco a la derecha muestra la caché de instrucción de nivel 1, también de 32 KB de tamaño. Como su nombre lo indica, almacena varios comandos listos para dividirse en microoperaciones más pequeñas .(generalmente denotado por μops) que las ALU deben ejecutarse. También hay una caché para ellos, que se puede clasificar como Nivel 0, porque es más pequeña (contiene solo 1,500 operaciones) y más cercana que las cachés L1.

Quizás se pregunte por qué estas SRAM son tan pequeñas. ¿Por qué no tienen un tamaño de megabytes? Juntos, los cachés de datos e instrucciones ocupan casi la misma área en el chip que los bloques lógicos principales, por lo que su aumento conducirá a un aumento en el área total del dado.

Pero la razón principal de su tamaño de varios kilobytes es que a medida que aumenta la capacidad de la memoria, aumenta el tiempo necesario para buscar y recuperar datos. La caché L1 debe ser muy rápida, por lo que existe una compensación entre tamaño y velocidad; en el mejor de los casos, se necesitan aproximadamente 5 ciclos de reloj para obtener datos de esta caché (más para valores de punto flotante).

Caché L2 de Skylake: 256KB SRAM

Pero si este fuera el único caché dentro del procesador, su rendimiento se encontraría con un obstáculo inesperado. Es por eso que hay otra capa de memoria integrada en los núcleos: la caché de nivel 2. Este es un bloque de almacenamiento generalizado que contiene instrucciones y datos.

Siempre es más grande que el nivel 1: en los procesadores AMD Zen 2 , se necesitan hasta 512 KB para proporcionar suficientes datos para cachés de nivel inferior. Sin embargo, el gran tamaño requiere sacrificio: se tarda aproximadamente el doble de tiempo en encontrar y transferir datos desde esta caché en comparación con el Nivel 1.

En los días del primer Intel Pentium, la caché de nivel 2 era un chip separado, ya sea instalado en una placa pequeña separada (como DIMM RAM) o integrado en la placa base principal. Poco a poco, se trasladó a la carcasa del propio procesador y, finalmente, se integró por completo en el cristal del chip; esto sucedió en la era de los procesadores como Pentium III y AMD K6-III.

Este logro pronto fue seguido por otro nivel de caché necesario para soportar niveles más bajos, y llegó justo a tiempo para el apogeo de los chips multinúcleo.

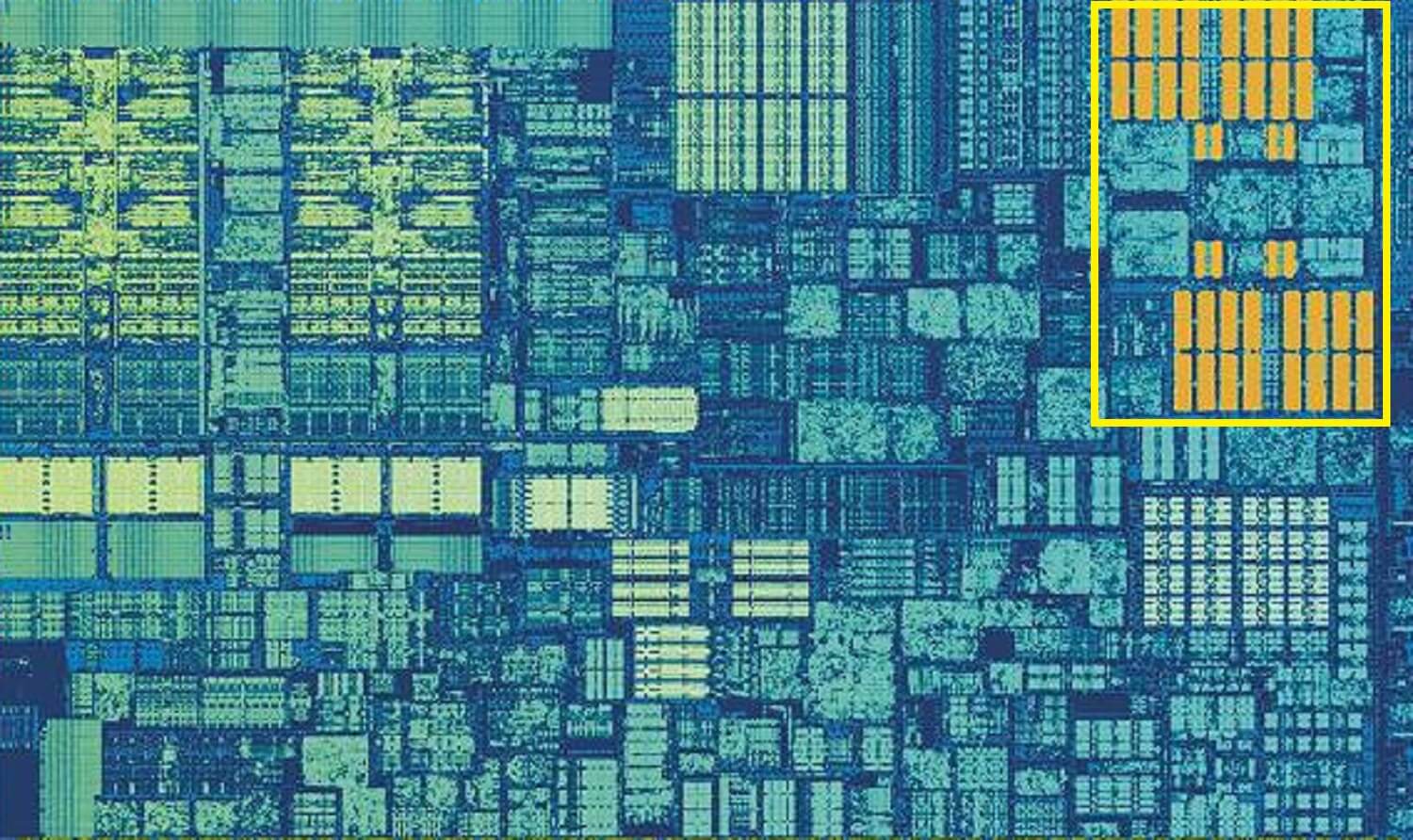

Chip Intel Kaby Lake. Fuente: Wikichip

Esta imagen del chip Intel Kaby Lake muestra cuatro núcleos a la izquierda (la GPU integrada ocupa casi la mitad del dado y está a la derecha). Cada núcleo tiene su propio conjunto "personal" de cachés de Nivel 1 y 2 (resaltados en cuadros blancos y amarillos), pero también tienen un tercer conjunto de bloques SRAM.

La caché de tercer nivel (Nivel 3), aunque se encuentra directamente al lado de un núcleo, es completamente común a todos los demás: cada núcleo puede acceder libremente al contenido de la caché L3 de otro núcleo. Es mucho más grande (2 a 32 MB), pero también mucho más lento, con un promedio de más de 30 ciclos, especialmente cuando el kernel necesita usar datos que residen en un bloque de caché lejano.

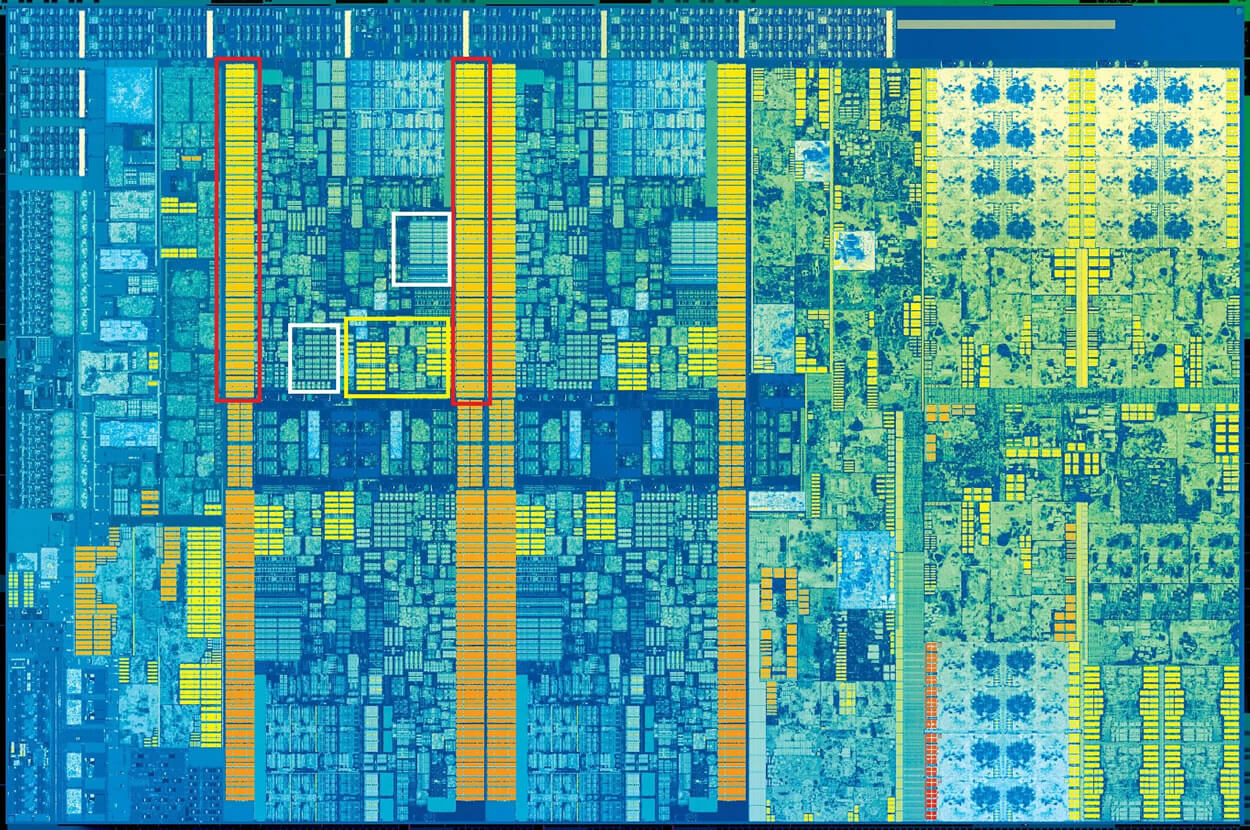

A continuación se muestra un núcleo de la arquitectura AMD Zen 2: cachés de instrucciones y datos de nivel 1 de 32 KB (en cuadros blancos), caché de nivel 2 de 512 KB (en cuadros amarillos) y un enorme bloque de caché L3 de 4 MB (en cuadro rojo).

Zoom en un solo núcleo de un procesador AMD Zen 2. Fuente: Fritzchens Fritz

Pero espera: ¿cómo pueden 32 KB ocupar más espacio físico que 512 KB? Si el nivel 1 almacena tan pocos datos, ¿por qué es desproporcionadamente grande en comparación con las cachés L2 y L3?

No solo números

La caché mejora el rendimiento al acelerar la transferencia de datos a bloques lógicos y al mantener cerca una copia de las instrucciones y los datos de uso frecuente. La información almacenada en la memoria caché se divide en dos partes: los datos en sí y el lugar donde se encuentra originalmente en la memoria / almacenamiento del sistema; esta dirección se denomina etiqueta de memoria caché .

Cuando el procesador realiza una operación que necesita leer o escribir datos desde / hacia la memoria, comienza verificando las etiquetas en la caché de nivel 1. Si los datos requeridos están allí (ocurrió un acierto de caché ), entonces estos datos son casi En seguida. Se produce una falta de caché cuando la etiqueta requerida no se encuentra en el nivel más bajo de la caché.

Se crea una nueva etiqueta en la caché L1, y el resto de la arquitectura del procesador se hace cargo, buscando en otros niveles de la caché (hasta el almacenamiento principal, si es necesario) los datos de esa etiqueta. Pero para liberar espacio en la caché L1 para esta nueva etiqueta, se debe agregar algo a L2.

Esto da como resultado una mezcla de datos casi constante, realizada en solo unos pocos ciclos de reloj. La única forma de lograr esto es creando una estructura compleja alrededor de SRAM para manejar la gestión de datos. En otras palabras, si el núcleo del procesador consistiera en solo una ALU, entonces el caché L1 sería mucho más simple, pero como hay docenas de ellos (y muchos de ellos hacen malabares con dos flujos de instrucciones), el caché requiere muchas conexiones para mover datos.

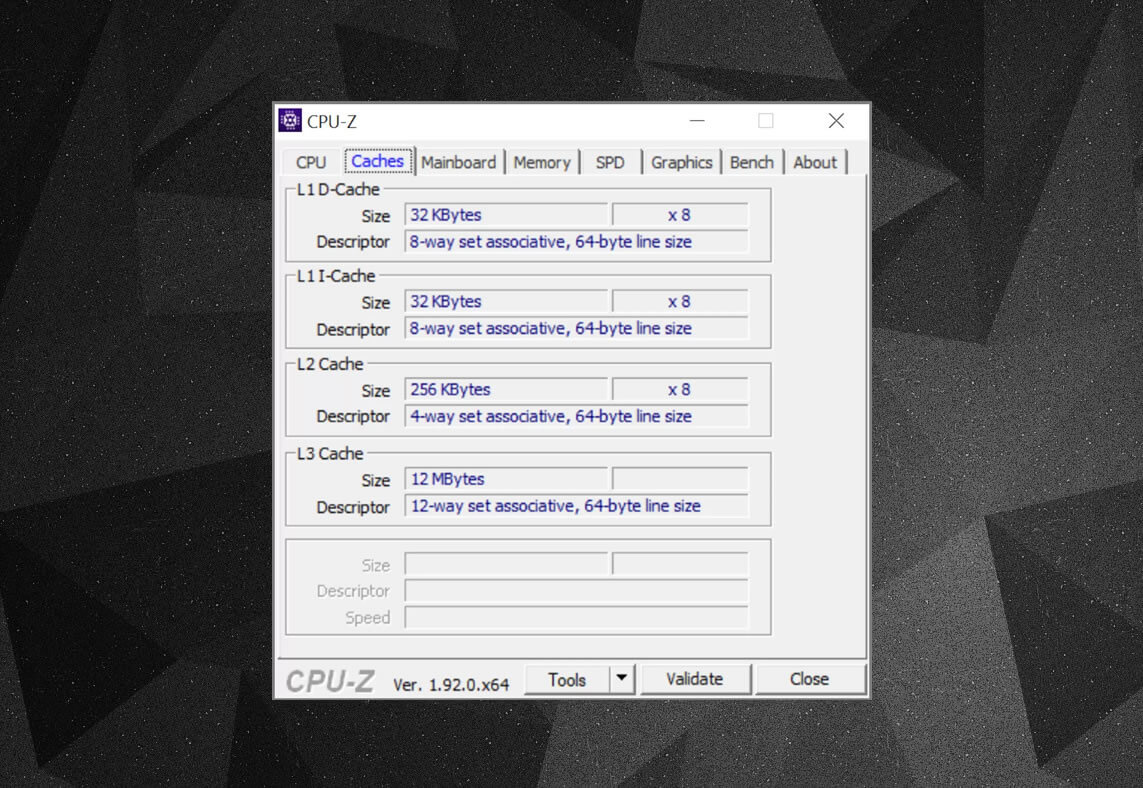

Puede utilizar software gratuito como CPU-Z para examinar la información de la caché en el procesador de su computadora . Pero, ¿qué significa toda esta información? Un elemento importante es la etiqueta asociativa de conjunto , que indica las reglas utilizadas para copiar bloques de datos de la memoria del sistema a la caché.

La información de caché anterior es para Intel Core i7-9700K . Cada uno de sus cachés de nivel 1 se divide en 64 pequeños bloques, llamados conjuntos , y cada uno de estos bloques también se divide en líneas de caché.(64 bytes de tamaño). "Conjunto asociativo" significa que un bloque de datos del sistema está vinculado a líneas de caché en un conjunto en particular, y no se puede vincular libremente a otro lugar.

"8 vías" significa que un bloque se puede asociar con 8 líneas de caché en el conjunto. Cuanto mayor sea el nivel de asociatividad (es decir, cuanto mayor sea el "camino"), más posibilidades de que se produzca un acierto en la memoria caché durante una búsqueda del procesador y menor pérdida causada por fallas en la memoria caché. Las desventajas de dicho sistema son el aumento de la complejidad y el consumo de energía, así como un menor rendimiento, porque se deben procesar más líneas de caché para cada bloque de datos.

Incluye caché L1 + L2, caché de víctima L3, políticas de escritura diferida, incluso ECC. Fuente: Fritzchens Fritz

Otro aspecto de la complejidad de la caché tiene que ver con cómo se almacenan los datos entre diferentes niveles. Las reglas se establecen en la política de inclusión . Por ejemplo, los procesadores Intel Core tienen cachés L1 + L3 totalmente inclusivos . Esto significa que algunos datos del Nivel 1, por ejemplo, pueden estar presentes en el Nivel 3. Puede parecer una pérdida de valioso espacio de caché, pero la ventaja es que si el procesador no detecta la etiqueta en el nivel inferior, no necesita buscar datos en el nivel superior.

En los mismos procesadores, la caché L2 no es inclusiva: todos los datos almacenados allí no se copian en ninguna otra capa. Esto ahorra espacio, pero hace que el sistema de memoria del chip busque una etiqueta faltante en L3 (que siempre es mucho más grande). Los cachés de víctimas tienen un principio similar, pero se utilizan para almacenar información transportada desde niveles inferiores. Por ejemplo, los procesadores AMD Zen 2 utilizan el caché de la víctima L3, que simplemente almacena datos de L2.

Existen otras políticas de caché, como escribir datos tanto en el caché como en la memoria principal del sistema. Se denominan políticas de escritura ; la mayoría de los procesadores modernos utilizan cachés de escritura diferida- esto significa que cuando se escriben datos en la capa de caché, hay un retraso antes de escribir una copia en la memoria del sistema. La mayoría de las veces, esta pausa dura mientras los datos permanezcan en el caché; la RAM recibe esta información solo cuando se "extrae" del caché.

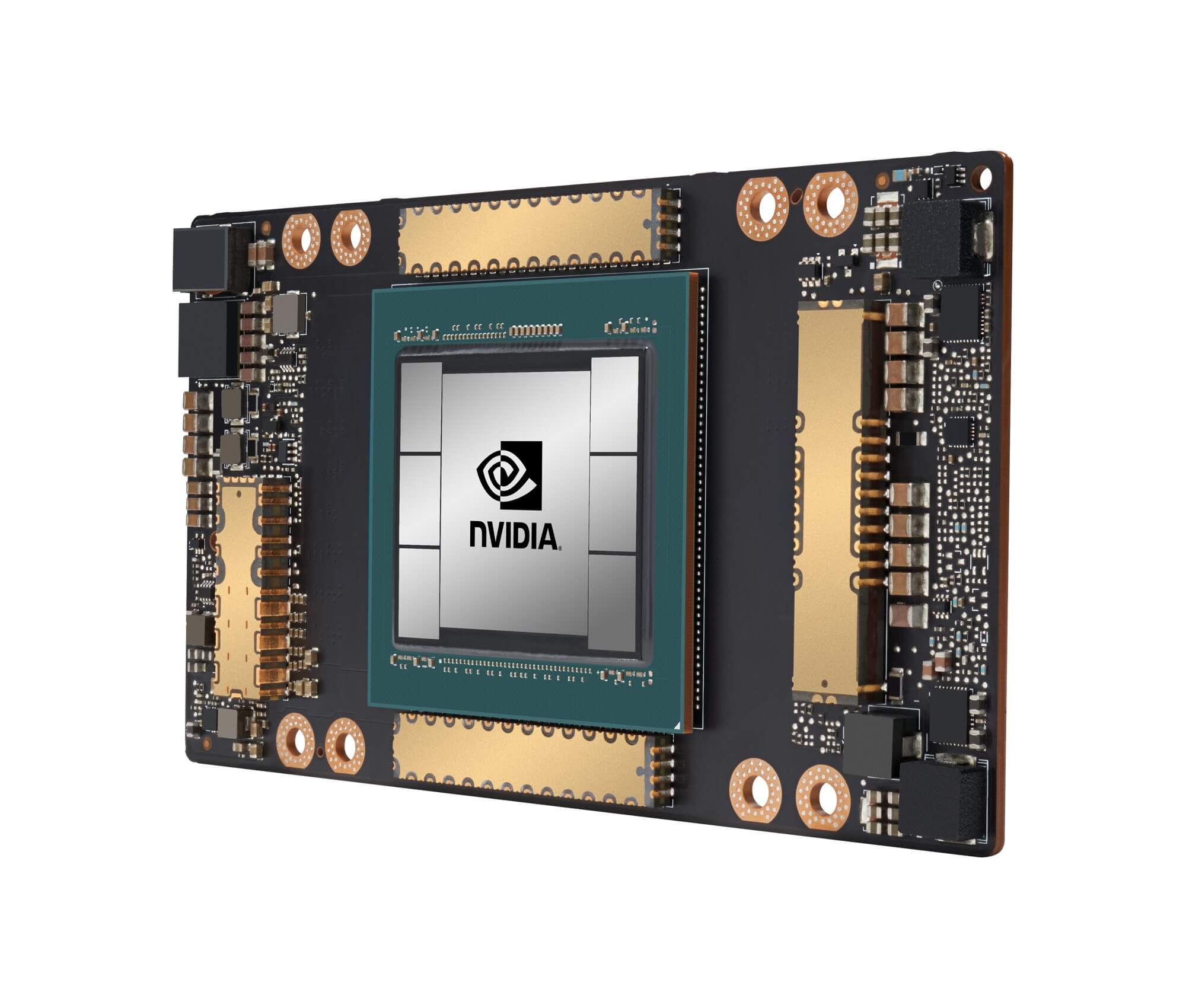

GPU Nvidia GA100 con 20 MB de caché L1 y 40 MB de caché L2

Para los diseñadores de procesadores, la elección del tamaño, el tipo y la política de la caché es una cuestión de equilibrar la unidad para aumentar la potencia del procesador con una mayor complejidad y huella de chip. Si fuera posible crear cachés asociativos de 1000 canales y 20 MB de nivel 1 para que no ocuparan el área de Manhattan (y no consumieran la misma cantidad de energía), ¡entonces todos tendríamos computadoras con tales chips!

El nivel más bajo de cachés en los procesadores modernos se ha mantenido prácticamente sin cambios durante la última década. Sin embargo, la caché de nivel 3 sigue aumentando de tamaño. Si tuvieras $ 999 para un Intel i7-980X hace diez años, podrías tener un caché de 12 MB. Hoy por la mitad de esa cantidaddisponible para la compra 64 MB .

Para resumir, el caché es un dispositivo absolutamente esencial e impresionante. No hemos cubierto otros tipos de cachés en la CPU y GPU (por ejemplo, búferes de traducción asociativos o cachés de texturas), pero como todos tienen la misma estructura simple y disposición de niveles, no será difícil entenderlos.

¿Ha tenido una computadora con caché L2 en la placa base? ¿Qué hay de las placas hijas Pentium II y Celeron (por ejemplo, 300a ) ranuradas ? ¿Recuerda su primer procesador L3 compartido?

Publicidad

Nuestra empresa ofrece en alquiler servidores con procesadores Intel y AMD. En el último caso, ¡estos son servidores épicos! VDS con AMD EPYC , frecuencia de núcleo de CPU de hasta 3,4 GHz. La configuración máxima es de 128 núcleos de CPU, 512 GB de RAM, 4000 GB de NVMe.