¿Quieres saber cómo conseguir un trabajo diseñando dispositivos electrónicos para naves espaciales? Recientemente recibí una oferta para entrevistarme para el puesto de diseñador de FPGA para Blue Origin (ver arriba). Personalmente, no necesito ese puesto (ya tengo un puesto de diseñador ASIC en otra empresa), pero noté que los requisitos técnicos para los solicitantes de Blue Origin coinciden exactamente con el contenido del seminario para escolares y estudiantes junior, que se llevará a cabo del 15 al 17 de septiembre. en la exposición ChipEXPO en Skolkovo , con el apoyo de RUSNANO. Aunque, por supuesto, en el seminario tocaremos las tecnologías Verilog y FPGA solo en el nivel inicial: conceptos básicos y ejemplos simples, pero ya interesantes. Para conseguir un trabajo después de eso en Blue Origin, todavía necesita varios años de estudio y trabajo.

Debido al coronavirus, el seminario será remoto, por lo que no solo los escolares y estudiantes de Moscú, sino también toda Rusia, Ucrania, Kazajstán, California y otros países y regiones podrán participar. Profesores e ingenieros de MIET, HSE MIEM, MIPT, la Universidad Politécnica de Chernihiv, la Universidad de Samara, IVA Technologies y fpga-systems.ru conducirán físicamente las conferencias y ayudarán de forma remota a los participantes .

Para participar primero, incluso antes del seminario, debe completar tres partes de un curso teórico de RUSNANO, bajo el título general "Cómo funcionan los creadores de nanochips inteligentes": "De transistor a microcircuito", "Lado lógico de los circuitos digitales", "Lado físico de los circuitos digitales". Este curso es fundamental para que entiendas lo que estás haciendo durante el taller. Al recibir un certificado de finalización del curso teórico en línea, puede ir a la oficina de RUSNANO en Moscú y recibir una tarifa gratuita para un seminario práctico (si se quedan, los escolares tienen prioridad). Con esta placa puede trabajar en casa, antes, durante y después del seminario de Skolkovo.

Cómo cobrar, prepararse para el seminario y qué habrá allí:

Puede encontrar instrucciones sobre cómo obtener una tarifa en el sitio web de STEMford . STEMford son programas educativos para escolares de eNano , una subsidiaria de la Fundación RUSNANO para Programas Educativos de Infraestructura. Esta es su oficina para visitar:

Antes del laboratorio, deberá tener Intel Quartus Prime Lite Edition instalado en su computadora. Las instrucciones sobre cómo hacer esto se encuentran en el fragmento libre del libro "Síntesis digital: Un curso práctico" editado por A. Yu. Romanov, Yu. V. Panchul. DMK Press, 2020.

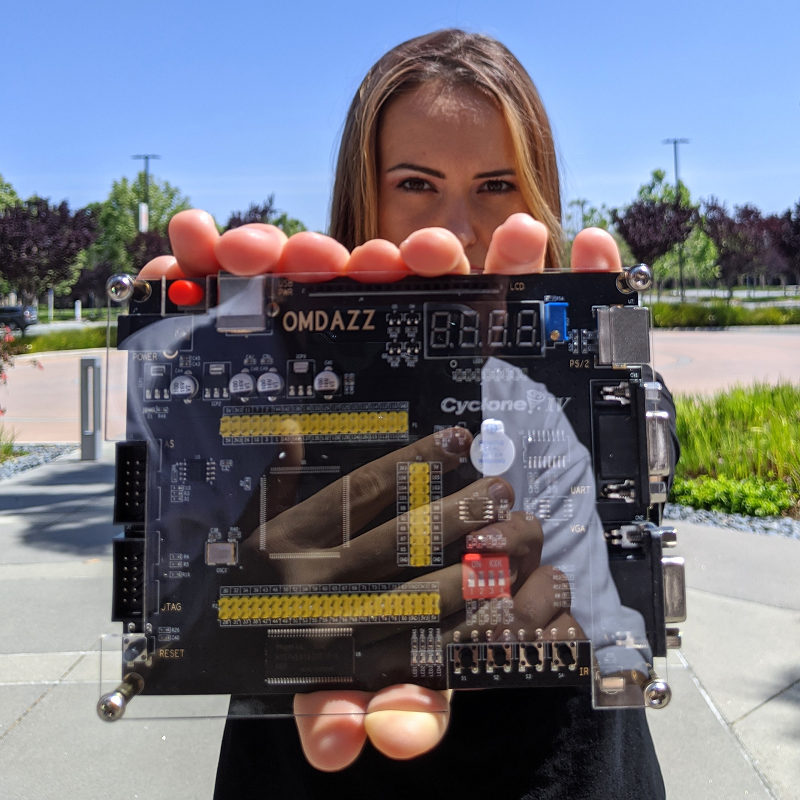

En general, "Digital Synthesis" es un libro útil para un seminario, describe ejercicios que se presentarán con algunas variaciones en el seminario, aunque por ejemplo, en lugar del procesador educativo schoolMIPS, un más modernoschoolRISCV : Al final del libro de Síntesis digital , hay una entrevista bastante divertida con una pareja de recién casados, Vladislav y Elena Sharshin, que, junto con su colega Andrey Papushin, Intel trajo a California para una victoria de plata en la competencia InnovateFPGA: Aquí está uno de los tableros que se usarán en el seminario. Si no hay suficientes tablas para ti, o si no eres un estudiante, puedes pedir una tabla en AliExpress y en otros lugares: 1 , 2 , 3 , 4 : ¿Qué pasará en el seminario? Estas son las partes del programa :

15 . .

: , « » ().

15.00. , .

15.15-15.30. -: Apple iPhone: .

, . , .

15.30-16.00. : Verilog. /FPGA Intel Quartus Prime Lite Edition. .

16.00-16.30.

///-, , c .

16.30-17.00. .

17.00-17.30. : , .

17.30-18.00. .

18.00-19.00. ZEOWAA OMDAZZ Intel FPGA Cyclone IV: : ( ). Terasic DE10-Lite Intel FPGA MAX10: : ( ).

19.00-21.00. , : , , ,

.

El primer día se basa en la experiencia de celebrar el seminario del año pasado en Moscú, que se describe en un artículo sobre Habré : El

segundo día se basa en la experiencia de realizar una escuela de verano en Zelenograd el año pasado y seminarios en Samara:

16 . .

: , , , .

15.00-15.15. -: : , .

.

15.15-15.30. : VGA.

.

15.30-16.00. .

16.00-16.30. . Digilent Basys3 Xilinx FPGA Artix-7. .

, fpga-systems.ru.

16.30-17.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

17.00-17.30. : Linear Feedback Shift Registers (LFSR) . Verilog VHDL LFSR . LFSR VGA .

, .

17.30-18.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

18.00-19.00. .

.

18.00-21.00. , . .

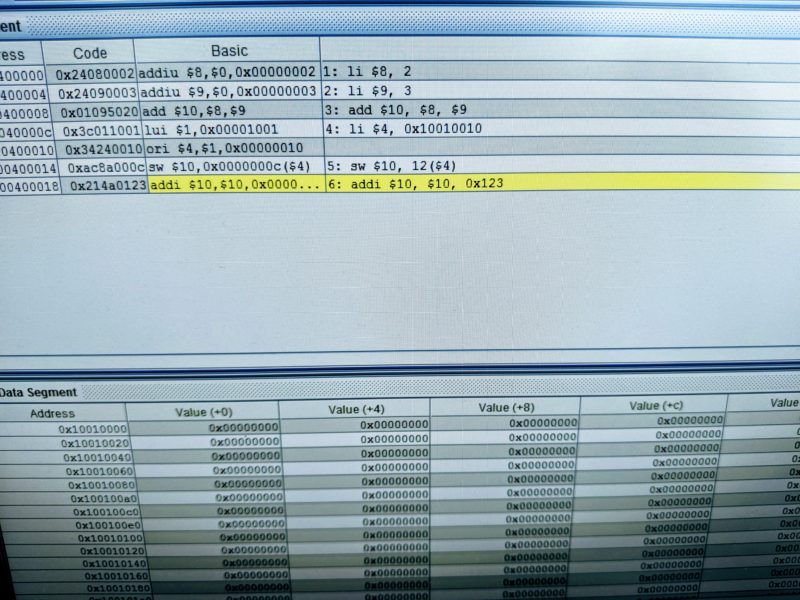

El tercer día se basará en la experiencia del programa educativo sobre procesadores de Stanislav Zhelnio y Alexander Romanov . Solo antes de que desarrollaran y usaran el procesador de aprendizaje schoolMIPS, y ahora usaremos schoolRISCV. La arquitectura RISC-V es muy similar a MIPS y otras arquitecturas RISC (SPARC, ARM, POWER, etc.), pero sin sus muletas, lo que tenía sentido en procesadores simples, pero interfiere con los complejos (registrar ventanas en SPARC, que no tienen sentido en software con una pila grande; ranuras de retardo de rama en MIPS hasta Rev6, que son buenas en una tubería estática simple con obtención secuencial de instrucciones, pero se convierten en un dolor de cabeza en una tubería dinámica, etc.

Dado que en Rusia hay al menos tres compañías que diseñan procesadores en la arquitectura RISC-V, y este es un buen candidato para un futuro procesador ruso de alta gama integrado y tal vez incluso de escritorio y servidor, y dado que RISC-V reemplaza con confianza a MIPS como un caballos para la experimentación arquitectónica y microarquitectura en las universidades del mundo, es mejor enseñarles a los escolares.

17 . .

— , ..., . .. (), « » ( ).

15.00-15.15. -: ENIAC , IBM/360 Cray-1 Intel, ARM RISC-V: , .

.

15.15-16.30. : . RISC-V .

, - .

16.30-17.30. : . schoolRISCV, . .

, IVA Technologies.

17.30-17.30. . .

.

17.30-18.00. Conferencia final: Los próximos pasos para dominar el diseño de circuitos digitales y aplicar este conocimiento al diseño integrado y los aceleradores de computación de inteligencia artificial.

Alexander Yurievich Romanov.

18.00-21.00. Ejercicios adicionales y proyectos individuales de los estudiantes sobre el cambio de procesador e integración con dispositivos periféricos. Con la ayuda de estudiantes de pregrado y posgrado de microelectrónica de las universidades participantes.

Aquí está Stanislav Zhelnio enseñando a escolares el verano pasado en Zelenograd: ¡

Nos vemos en un seminario en el ChipEXPO virtual en Skolkovo! Intentaremos realizar una parte del evento allí y en vivo, con la ayuda de los maestros de MIET, HSE MIEM y MIPT, pero si el virus no lo permite, lo realizaremos de manera distribuida.