Introducción

Las limitaciones de tiempo son cierta información, mediante la cual la utilidad de análisis de tiempo en el sistema CAD puede calcular si los datos pasarán con éxito por todos los registros del proyecto. El usuario debe calcular estos límites él mismo y anotarlos en el archivo de límites de tiempo. Sin estas restricciones, el usuario escribe un proyecto al azar, sin comprobar su rendimiento, y el compilador jurará que no ha encontrado ninguna restricción.

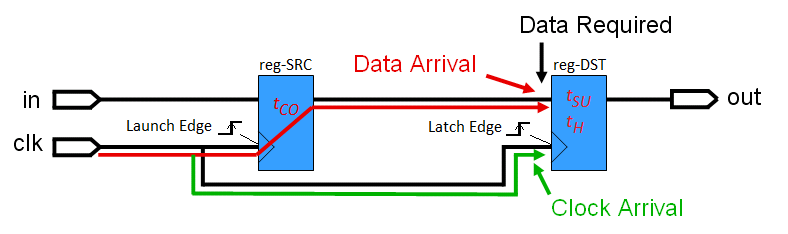

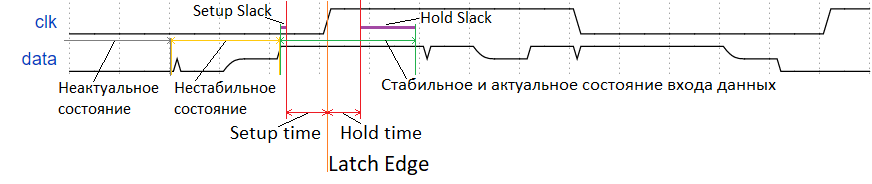

En el artículo anterior ( enlace) Hablé sobre qué es la transferencia de datos entre dos registros y cómo se calcula la ejecución de las relaciones de tiempo en el caso de la transferencia de datos dentro de la FPGA, cuando ambos registros en consideración, las rutas de las señales de reloj y las señales de datos se encuentran dentro de la FPGA. A partir de ese artículo, es necesario obtener una comprensión del concepto de lógica síncrona como una red tejida a partir de una multitud de transferencias entre registros (Fig. 1) y el término "holgura" (Fig. 2).

En este artículo, consideraremos casos de transferencia de datos, en los que uno de los dos registros de transferencia está fuera de la FPGA, este es un registro de un dispositivo externo, un microcontrolador, ADC, etc.

Figura: 1. El esquema de transferencia de datos entre registros desde el registro de origen (origen) al registro de destino (destino).

Figura: 2. El significado de holguras en relación con el frente de captura en la entrada del registro de recepción.

Fórmulas generales para el cálculo de holguras, derivadas del artículo anterior:

minSmittupagsSlunCk=minreuntunRmiqtuyormire-maxreuntunUNrryovunl=

=SR+mintCLKtoreST-maxtCLKtoSRC-maxtSU-maxtCO-maxtre

minHolreSlunCk=minreuntunUNrryovunl-maxreuntunRmiqtuyormire=

=-HR+mintCLKtoSRC-maxtCLKtoreST+mintCO-maxtH+mintre

Repasemos los términos.

La holgura es un margen de tiempo. Debe ser positivo.

Tiempo preestablecido (tiempo de configuración,tSU) - el tiempo mínimo que los datos ya deben estar en la entrada del registro de recepción en el momento en que el frente del reloj llega a la entrada del reloj del receptor.

Mantenga el tiempo (mantenga el tiempo,tH) Es el tiempo mínimo que los datos deben mantenerse en la entrada del receptor después de que el frente del reloj llega a la entrada del reloj del receptor.

Registrar el tiempo de respuesta (tiempo de reloj a salida,tCO) Es el tiempo desde la llegada del frente de reloj a la entrada de reloj del registro fuente hasta la aparición de nuevos datos estables en su salida.

SR y HR son la relación de configuración y retención, la diferencia entre los momentos del frente de captura y el frente del disparador en la fuente del reloj, teniendo en cuenta la inestabilidad. En el caso de analizar transmisiones FPGA internas, solo se toman los flancos ascendentes del reloj, por lo que esta expresión se simplifica aSR=T-CSU,HR=CHU... Pero las interfaces a menudo usan diferentes frentes, por lo que se debe usar una representación más general.

El jitter del reloj preestablecido / retenido (CSU / CHU) es una medida del jitter del reloj. En los cálculos, lleva el significado de un margen "por si acaso" para tener en cuenta los fenómenos causados por la frecuencia imperfecta del coágulo.

tre Es el tiempo que tarda la señal de datos en viajar entre registros.

tCLKtoSRCEs el tiempo que tarda el flanco de la señal de reloj en viajar desde la fuente de reloj hasta la entrada de reloj del registro de fuente. Y desde la fuente del reloj hasta el registro de destino, respectivamentetCLKtoreST...

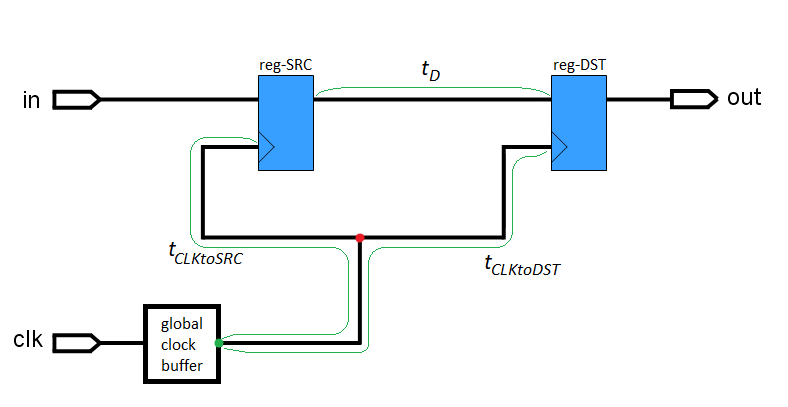

Las rutas de las señales se ilustran en la Figura 3.

Fig. 3. Designación del tiempo de viaje de las trayectorias de señales y datos de reloj.

En esta imagen, vemos dos puntos: verde y rojo. Ambos son puntos en los que las rutas del fragmento fuente y el fragmento receptor aún no han divergido. El punto verde es la salida del búfer de reloj global, el punto de entrada a la red de reloj global de la FPGA, con respecto al cual las entradas de reloj de todos los registros son aproximadamente equidistantes. El punto rojo es un punto arbitrario en la red del reloj global, en el que, como en la entrada de la red, el reloj aún no se ha dividido en dos copias de sí mismo, que han pasado a registros diferentes. Pero solo el punto verde es un punto adecuado para empezar a contar los tiempos para el paso de los relojes, porque está en uno de los lugares comprensibles para el compilador. En este ejemplo, a la entrada de la red de reloj global. Pero en el caso de interfaces simples que se sincronizan desde el exterior, el punto verde puede ser solo un tramo FPGA.El compilador conoce los tiempos desde este punto hasta cada uno de los registros. Y el punto rojo, el lugar donde coinciden accidentalmente los recorridos de los dos relojes analizados, no es adecuado para el punto de partida.

Tipos de transmisiones analizadas

Clasifiquemos los casos para el análisis temporal. El análisis se realiza por separado para cada tramo de FPGA con respecto a un determinado bloque. Como resultado del análisis, se evalúa la capacidad del tramo para enviar o recibir datos correctamente. La interfaz externa para el intercambio de datos sincrónico entre la FPGA y un dispositivo externo consta de varias líneas conectadas a las patas. De estos, una línea es la línea de trituración. Debe compartirse entre registros de ambos lados. Las líneas restantes, una o muchas, son líneas de entrada o salida unidireccionales. Lo que es una línea de entrada para un FPGA es una línea de salida para un dispositivo externo y viceversa. En este artículo, consideramos solo los casos más simples de análisis temporal, por lo que no tocamos las interfaces asíncronas y autotemporizadas, así como el uso de líneas de E / S bidireccionales.

Los casos de análisis se pueden clasificar por la dirección de los datos en relación con la FPGA (entrada / salida) y por la dirección del reloj en relación con la FPGA (los datos se sincronizan desde la FPGA / desde una fuente externa). Para cada caso, hay dos tipos de análisis (Configuración / Retención). En total, cuatro casos para análisis y ocho ecuaciones que necesitamos derivar.

Salida de datos sincronizados por un reloj FPGA interno

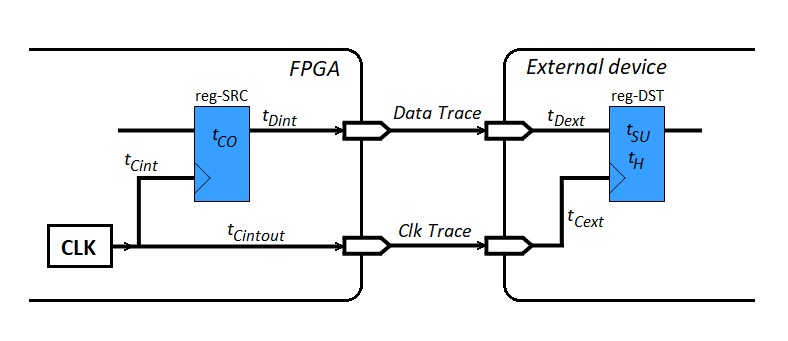

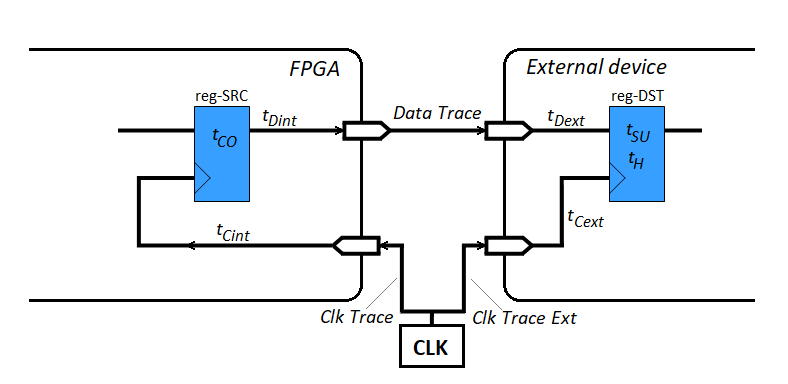

Considere el caso en el que necesitamos dar algo en nuestro fragmento (Fig. 4).

El esquema básico de transferencia de datos no ha cambiado. Pero los registros ahora pertenecen a dos microcircuitos diferentes, y la ruta de datos entre ellos no es lógica combinacional, sino solo pistas en la placa. Y nuestra tarea es adaptar las fórmulas de holgura conocidas a una situación ligeramente diferente.

Figura: 4. Transferencia de datos hacia afuera en su propio reloj FPGA.

En la Figura 4, vemos un esquema de transferencia entre registros. Muestra los tiempos de los procesos asociados con cada uno de los registros y los tiempos en los que las señales viajan por los caminos.

Configuré la siguiente indexación: la hora que hace referencia a los datos está marcada con la letra D. La hora que hace referencia al reloj está marcada con la letra C. Si ocurre un evento dentro de la FPGA, entonces su hora está marcada con un índice "int", y si en un dispositivo externo, entonces "ext" ... El tiempo que tarda el fragmento en viajar desde la fuente del fragmento hasta el vástago de salida del fragmento tiene el índice más largo "Cintout". DataTrace y ClkTrace son los tiempos de viaje de las trazas correspondientes en la PCB. El bloque "CLK" simboliza una especie de fuente interna de relojes.

La característica principal de las cantidades mencionadas en la figura es que todas son positivas. Todos ellos son iguales a la duración absoluta de cualquier proceso físico, lo que significa que físicamente solo pueden ser valores positivos. Esto es importante para un mayor razonamiento.

Ahora veremos más de cerca el análisis de la holgura preestablecida. Al observar la Figura 4, podemos correlacionar fácilmente los valores observados con los términos de las fórmulas de holgura:

Ahora sustituyamos estas igualdades en la fórmula de holgura preestablecida:tCLKtoSRC=tCyonortet

tre=treyonortet+reuntunTrunCmi+tremiXt

tCLKtoreST=tCyonortetotut+ClkTrunCmi+tCmiXt

minSmittupagsSlunCk=minreuntunRmiqtuyormire-maxreuntunUNrryovunl=

=SR+mintCLKtoreST-maxtCLKtoSRC-maxtSU-maxtCO-maxtre=

=SR+min(tCyonortetotut+ClkTrunCmi+tCmiXt)-max(tCyonortet)-tSU-tCO-

-max(treyonortet+reuntunTrunCmi+tremiXt)

Ahora estamos usando el conocimiento de que todos los términos entre paréntesis son mayores que cero. Entonces sabemos cómo abrir tales corchetes: el mínimo de la suma es igual a la suma de los mínimos, y el máximo de la suma es igual a la suma de los máximos:

minSmittupagsSlunCk=SR+mintCyonortetotut+minClkTrunCmi+mintCmiXt-maxtCyonortet-

-tSU-tCO-maxtreyonortet-maxreuntunTrunCmi-maxtremiXt

Ahora reorganicemos los términos en lugares para agrupar los términos de los procesos dentro de la FPGA y los procesos dentro del dispositivo externo entre paréntesis:

minSmittupagsSlunCk=SR-(maxtCyonortet+tCO+maxtreyonortet-mintCyonortetotut)+

+minClkTrunCmi-maxreuntunTrunCmi-(maxtremiXt+tSU-mintCmiXt)

¿Qué vemos entre paréntesis? Si observa de cerca y recuerda una vez más que todos los valores especificados son mayores que cero, entonces podemos decir que vemos una expresión de cierto tiempo de respuesta equivalente (con un asterisco) del registro FPGA y el tiempo de preajuste equivalente del registro del dispositivo externo:

maxtCyonortet+tCO+maxtreyonortet-mintCyonortetotut=maxt∗CO

maxtremiXt+tSU-mintCmiXt=maxt∗SU

minSmittupagsSlunCk=SR-maxt∗CO+minClkTrunCmi-maxreuntunTrunCmi-maxt∗SU

¿Por qué no usamos valores equivalentes si los fabricantes de chips ya nos los han calculado, teniendo en cuenta sus retrasos internos? El compilador calculará los valores equivalentes en el lado de FPGA sin la intervención del usuario, y los valores equivalentes del dispositivo externo se indican explícitamente en la hoja de datos del dispositivo.

Ahora echemos un vistazo más de cerca a la última expresión. En él, los tres primeros términos ya son conocidos por el analizador, porque ya le hemos indicado la frecuencia de funcionamiento y la magnitud de la inestabilidad. El compilador ha rastreado y el analizador conoce el tiempo de respuesta equivalente de su registro. Esto significa que el analizador conoce la duración de todos los procesos dentro de la FPGA. Pero los últimos tres términos son únicos para cada tramo y el usuario debe calcularlos él mismo e indicarlos al analizador como un número. ¿Cual es este numero? Echando un vistazo más de cerca a los últimos tres términos, veremos que pueden interpretarse como un máximo negativo de un cierto valor:

minClkTrunCmi-maxreuntunTrunCmi-maxt∗SU=-maxOtutpagstutremiluny

Y este valor es significativamente igual al retraso de todo lo que sucede fuera de la FPGA, en relación con todo lo que sucede dentro. Se llama así: retardo de salida, retardo de salida.

Resumamos:

minSmittupagsSlunCk=SR-maxt∗CO-maxOtutpagstutremiluny

maxOtutpagstutremiluny=maxreuntunTrunCmi+maxt∗SU-minClkTrunCmi=

=max(reuntunTrunCmi+t∗SU-ClkTrunCmi)

Ahora derivaremos una ecuación similar para la holgura de retención. Recuerde la ecuación general y sustituya nuevos términos en ella:

Abramos los corchetes y agrupemos inmediatamente los términos alrededor de cada uno de los registros:minHolreSlunCk=minreuntunUNrryovunl-maxreuntunRmiqtuyormire=

=-HR+mintCLKtoSRC-maxtCLKtoreST+mintCO-maxtH+mintre=

=-HR+min(tCyonortet)-max(tCyonortetotut+ClkTrunCmi+tCmiXt)+tCO-tH+

+min(treyonortet+reuntunTrunCmi+tremiXt)

Y nuevamente vemos cómo los términos se agrupan en cantidades equivalentes, esta vez tCO y tH:minHolreSlunCk=-HR+(tCO+mintCyonortet+mintreyonortet-maxtCyonortetotut)-

-maxClkTrunCmi+minreuntunTrunCmi-(tH-mintremiXt+maxtCmiXt)

Y los tres últimos términos se pueden entender como el mínimo retraso externo:minHolreSlunCk=-HR+mint∗CO+minreuntunTrunCmi-maxClkTrunCmi-maxt∗H

minreuntunTrunCmi-maxClkTrunCmi-maxt∗H=minOtutpagstutremiluny

Resumamos:

minHolreSlunCk=-HR+mint∗CO+minOtutpagstutremiluny

minOtutpagstutremiluny=min(reuntunTrunCmi-ClkTrunCmi-t∗H)

Cabe destacar que minOtutpagstutremiluny y maxOtutpagstutremiluny- este es el mínimo y el máximo, no absolutamente el mismo valor. Cada análisis preestablecido y análisis de retención considera diferentes situaciones y diferentes retrasos externos. Esto significa que los términos, como puede verse en las fórmulas, se toman de manera diferente.

Salida de datos sincronizados por un reloj externo

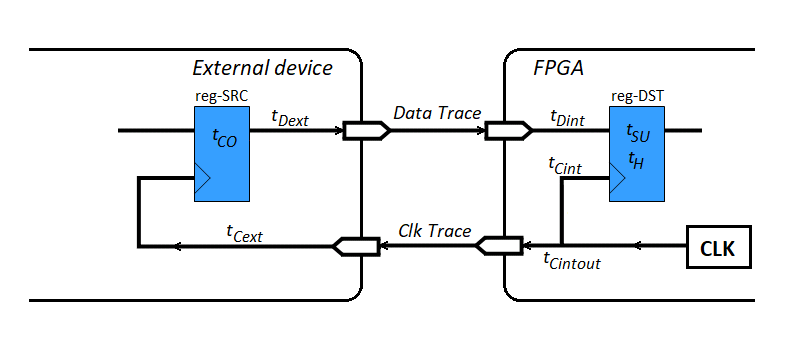

Ahora pasemos al caso en el que necesitamos darle algo al exterior, pero según un reloj externo a la FPGA (Fig. 5). En general, la fuente de reloj está ubicada fuera de la FPGA, en particular, puede estar dentro de un dispositivo externo.

Figura: 5. Transferencia de datos al exterior a través de un reloj externo.

En la Figura 5, vemos la fuente del fragmento afuera. En consecuencia, la cantidadtCyonortetotuty apareció el tiempo para el paso del fragmento al dispositivo externo "Clk Trace Ext".

Al observar la Figura 5, correlacionamos los valores observados con los términos de las fórmulas generales de holgura:

tCLKtoSRC=ClkTrunCmi+tCyonortet

tre=treyonortet+reuntunTrunCmi+tremiXt

tCLKtoreST=ClkTrunCmimiXt+tCmiXt

Usando estas expresiones, abrimos los términos en la fórmula de holgura preestablecida, los agrupamos inmediatamente por registros y obtenemos la forma equivalente:

minSmittupagsSlunCk=minreuntunRmiqtuyormire-maxreuntunUNrryovunl=

=SR+mintCLKtoreST-maxtCLKtoSRC-maxtSU-maxtCO-maxtre=

=SR-(maxtCyonortet+tCO+maxtreyonortet)-maxreuntunTrunCmi-

-(maxtremiXt+tSU-mintCmiXt)-maxClkTrunCmi+minClkTrunCmimiXt=

=SR-maxt∗CO-max(t∗SU+reuntunTrunCmi+ClkTrunCmi-ClkTrunCmimiXt)

minSmittupagsSlunCk=SR-maxt∗CO-maxOtutpagstutremiluny

maxOtutpagstutremiluny=max(t∗SU+reuntunTrunCmi+ClkTrunCmi-ClkTrunCmimiXt)

Analizamos la holgura de retención de la misma manera:

minHolreSlunCk=minreuntunUNrryovunl-maxreuntunRmiqtuyormire=

=-HR+mintCLKtoSRC-maxtCLKtoreST+mintCO-maxtH+mintre=

=-HR+(mintCyonortet+tCO+mintreyonortet)+minreuntunTrunCmi+minClkTrunCmi-

-(tH-mintremiXt+maxtCmiXt)-maxClkTrunCmimiXt=

=-HR+mint∗CO+minreuntunTrunCmi+minClkTrunCmi-maxClkTrunCmimiXt-maxt∗H

minHolreSlunCk=-HR+mint∗CO+minOtutpagstutremiluny

minOtutpagstutremiluny=min(reuntunTrunCmi+ClkTrunCmi-ClkTrunCmimiXt-t∗H)

Si en este esquema consideramos un caso particular (pero frecuente), cuando la fuente del truco está dentro de un dispositivo externo, entonces las fórmulas derivadas cambiarán solo por el hecho de que ClkTraceExt se vuelve igual a cero en ellas. Mover la fuente del fragmento al interior del dispositivo externo provocará en nuestros cálculos una dispersión microscópica del fragmento dentro del dispositivo externo entre la salida del reloj y el registro, pero será tenido en cuenta por el fabricante del dispositivo externo y se incluirá en los valores equivalentes.t∗SU y t∗H...

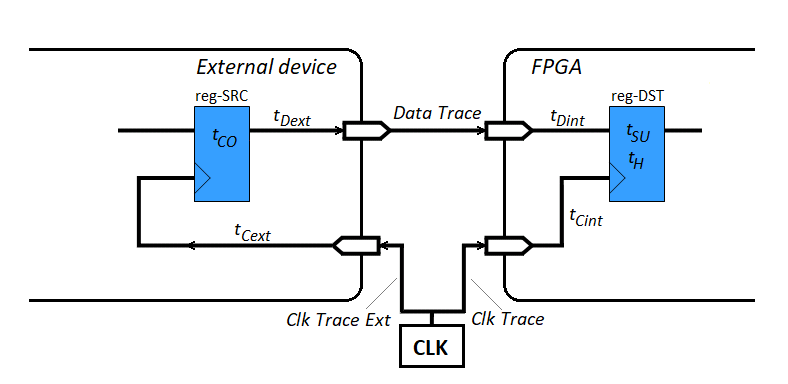

Entrada de datos sincronizados por un reloj FPGA interno

Pasamos ahora a considerar los tramos de entrada de la interfaz síncrona. La FPGA y el dispositivo externo de la Figura 6 se intercambian.

Figura: 6. Recibir datos en su propio reloj FPGA.

El análisis de tal esquema no es más complicado que los anteriores.

Revelamos, agrupamos ...tCLKtoSRC=tCyonortetotut+ClkTrunCmi+tCmiXt

tre=tremiXt+reuntunTrunCmi+treyonortet

tCLKtoreST=tCyonortet

Y obtenemos el valor del retardo externo, que esta vez llamaremos input:minSmittupagsSlunCk=minreuntunRmiqtuyormire-maxreuntunUNrryovunl=

=SR+mintCLKtoreST-maxtCLKtoSRC-maxtSU-maxtCO-maxtre=

=SR-(tSU+maxtreyonortet-mintCyonortet+maxtCyonortetotut)-maxreuntunTrunCmi-

-(tCO+maxtremiXt+maxtCmiXt)-maxClkTrunCmi

minSmittupagsSlunCk=SR-maxt∗SU-maxyonortepagstutremiluny

maxyonortepagstutremiluny=max(reuntunTrunCmi+t∗CO+ClkTrunCmi)

Ahora la holgura de retención:

minHolreSlunCk=minreuntunUNrryovunl-maxreuntunRmiqtuyormire=

=-HR+mintCLKtoSRC-maxtCLKtoreST+mintCO-maxtH+mintre=

=-HR-(tH-mintreyonortet+maxtCyonortet-mintCyonortetotut)+minreuntunTrunCmi+

+(tCO+mintremiXt+mintCmiXt)+minClkTrunCmi

minHolreSlunCk=HR-maxt∗H+minyonortepagstutremiluny

minyonortepagstutremiluny=min(t∗CO+reuntunTrunCmi+ClkTrunCmi)

Introducción de datos cronometrados por un reloj externo

Además, de acuerdo con el moleteado, observamos el esquema de transferencia de datos y revelamos los términos de la fórmula general.

Figura: 7. Recepción de datos en relojes externos.

tCLKtoSRC=ClkTrunCmimiXt+tCmiXt

tre=tremiXt+reuntunTrunCmi+treyonortet

tCLKtoreST=ClkTrunCmi+tCyonortet

Fórmula de holgura preestablecida:

minSmittupagsSlunCk=minreuntunRmiqtuyormire-maxreuntunUNrryovunl=

=SR+mintCLKtoreST-maxtCLKtoSRC-maxtSU-maxtCO-maxtre=

=SR-(tSU+maxtreyonortet-mintCyonortet)-maxreuntunTrunCmi-

-(tCO+maxtremiXt+maxtCmiXt)-maxClkTrunCmimiXt+minClkTrunCmi=

=SR-maxt∗SU-max(t∗CO+reuntunTrunCmi+ClkTrunCmimiXt-ClkTrunCmi)

minSmittupagsSlunCk=SR-maxt∗SU-maxyonortepagstutremiluny

maxyonortepagstutremiluny=max(t∗CO+reuntunTrunCmi+ClkTrunCmimiXt-ClkTrunCmi)

Fórmula de retención de holgura:

minHolreSlunCk=minreuntunUNrryovunl-maxreuntunRmiqtuyormire=

=-HR+mintCLKtoSRC-maxtCLKtoreST+mintCO-maxtH+mintre=

=-HR-(tH-mintreyonortet+maxtCyonortet)+minreuntunTrunCmi+

+(tCO+mintremiXt+mintCmiXt)+minClkTrunCmimiXt-maxClkTrunCmi

minHolreSlunCk=-HR-maxt∗H+minyonortepagstutremiluny

minyonortepagstutremiluny=min(t∗CO+reuntunTrunCmi+ClkTrunCmimiXt-ClkTrunCmi)

Nuevamente, si la fuente del reloj está dentro de un dispositivo externo, simplemente equipare ClkTraceExt a cero.

Interpretación visual

Las fórmulas son ciertamente buenas, pero si te sumerges en este tema por primera vez, las fórmulas parecen incomprensibles, sin vida. Me gustaría algo más claro para que las fórmulas adquieran un significado visible. Bien, analicemos el significado físico de las fórmulas, tomando como ejemplo el caso de salida de datos por un reloj externo . Permítanme recordarles cómo se ven el diagrama y las fórmulas:

Fig. 8. Transferencia de datos al exterior a través de un reloj externo.

minSmittupagsSlunCk=minreuntunRmiqtuyormire-maxreuntunUNrryovunl=

=SR-maxt∗CO-maxt∗SU-maxreuntunTrunCmi-maxClkTrunCmi+minClkTrunCmimiXt

minHolreSlunCk=minreuntunUNrryovunl-maxreuntunRmiqtuyormire=

=-HR+mint∗CO+minreuntunTrunCmi+minClkTrunCmi-maxClkTrunCmimiXt-maxt∗H

Durante la transferencia de datos, ocurren dos eventos: el registro de origen se activa y el registro de destino se activa. Los eventos ocurren porque son desencadenados por los frentes de reloj que emergen de la fuente de reloj. A partir de aquí comenzaremos a buscar.

La fuente del reloj genera un frente de inicio y llega a la FPGA durante ClkTrace. Entonces el registro FPGA se activa durantet∗CO... Además, los nuevos datos generados por este disparador van desde la FPGA al dispositivo externo durante el DataTrace.

Por otro lado, la fuente del reloj también genera el frente de captura, que llega al dispositivo externo durante ClkTraceExt.

Estos dos eventos ocurren en la entrada de datos de un dispositivo externo. Y aquí es importante que los datos lleguen allí antes de que el registro receptor comience a capturar. Deberían venir con al menos un tiempo restante.t∗SU, o mejor aún. Se considera el peor de los casos para garantizar que esto sea cierto. Si hay una reserva incluso en el peor de los casos, definitivamente todo está en orden. Por lo tanto, el peor momento de llegada de datos es el último momento,max(ClkTrunCmi+t∗CO+reuntunTrunCmi)... Y el peor momento de espera de datos es el momento más temprano,minClkTrunCmimiXt-maxt∗SU... E incluso en el peor de los casos, el segundo momento debería ser posterior al primero:

Con suerte, esta explicación arroja más luz sobre lo que está sucediendo.LuntChmiregramomi+minClkTrunCmimiXt-maxt∗SU>

>LuntunorteChmiregramomi+max(ClkTrunCmi+t∗CO+reuntunTrunCmi)

En esta expresión, vemos los momentos de los frentes: LaunchEdge y LatchEdge, que generalmente están ocultos en los términos SR y HR. Recordemos lo que es. Se consideran cuatro bordes en el análisis de preestablecimiento y retención:

Configurar Launch Edge: el borde que hará que la fuente envíe datos que el receptor debería capturar.

Hold Launch Edge es el frente que obligará a la fuente a enviar los siguientes datos, lo que puede evitar que el destinatario tome los anteriores. Por definición, siempre hay un período de reloj entre Setup LaunchEdge y Hold Launch Edge.

El Setup Latch Edge es el frente que obligará al receptor a capturar datos de entrada.

Hold Latch Edge es el mismo Setup Latch Edge. Es decir, de hecho, Latch Edge es físicamente uno, simplemente se le dan dos nombres para la belleza en dos tipos de análisis.

Dentro de los FPGA, la lógica síncrona generalmente solo funciona en flancos ascendentes (Figura 9). En este caso, desde el punto de vista del análisis de holgura, los ajustes preestablecidos de Setup Launch Edge y Setup Latch Edge están separados entre sí por un período de reloj, y desde el punto de vista del análisis de retención, Hold Launch Edge y Hold Latch Edge coinciden.

Figura: 9. Disposición mutua de los flancos en el caso de que ambos registros estén sincronizados por los flancos ascendentes.

Sin embargo, nadie prohíbe poner una señal de reloj invertida en la entrada de reloj de uno de los dos registros y así hacer que funcione en el flanco descendente del reloj. Esto, por cierto, a menudo se hace en las mismas interfaces SPI. Echemos un vistazo más de cerca a esta opción.

Considere la situación de sacar datos de la FPGA mediante un reloj externo, pero uno de los dos registros opera en un reloj invertido, es decir, a lo largo de un flanco descendente. Sea un registro de recepción en un dispositivo externo. Entonces, los roles de los frentes en el tiempo se distribuirán de manera diferente (Fig. 10).

Figura: 10. Disposición mutua de frentes en el caso de que la fuente sea sincronizada por el borde ascendente y el receptor por el borde descendente.

Esta inclusión de registros le permite alinear el tamaño de las holguras para preestablecer y mantener. Si los registros trabajaran desde los frentes de la misma dirección, entonces, debido a la escasa, en comparación con el período del reloj, la propagación de señales a lo largo de las pistas de la placa, la holgura preestablecida sería enorme y la holgura de retención sería muy pequeña.

La Figura 11 muestra la sincronización del reloj en la fuente del reloj. Para simplificar la figura, no especifiqué el término ClkTraceExt. Supondremos que la fuente del fragmento está dentro de un dispositivo externo.

Figura: 11. La posición de las holguras en el tiempo con respecto a los frentes de los relojes en el caso en que el receptor esté sincronizado por el flanco descendente.

En esta imagen, llegada máxima de datos- este es el último momento en que los datos pueden llegar a la entrada del receptor. El momento más temprano en el que los datos ya deberían estar en la entrada del receptor es el mínimo de datos requeridos . El último momento en el que los datos aún deben estar en la entrada del receptor es el máximo de datos requeridos . Y el momento más temprano en el que los datos ya pueden salir de la entrada del destinatario, siendo reemplazados por los datos siguientes, se denomina Salida mínima de datos .

Ahora las fórmulas y sus términos deberían ser más claros.

Cómo utilizar las fórmulas resultantes

Hemos obtenido fórmulas para retrasos externos y podemos calcular números específicos de retrasos para ajustarlos al archivo de restricciones de tiempo. Estas fórmulas constan globalmente de dos tipos de términos: las características de sincronización de los puertos del dispositivo externo y la latencia en las pistas de la placa.

Las especificaciones de puerto se encuentran generalmente en hojas de datos en secciones tituladas como "Características eléctricas / Especificaciones de CA / Requisitos de tiempo". A veces, estas características reciben diferentes nombres y hay que ser inteligente para encontrarlas. Pero las tablas con números suelen ir acompañadas de gráficos de tiempo que te permitirán identificar el parámetro que deseas. Un matiz importante, que puede resultar confuso, en las hojas de datos de muchos microcircuitos, los pines de salida a menudo se describen mediante los parámetros "Configurar el tiempo de salida" y "Mantener el tiempo de salida". En las fórmulas de este artículo, se deben comparar de la siguiente manera:tSUO=maxt∗CO,tHO=mint∗CO...

Con las pistas, es un poco más complicado. El cálculo exacto de la latencia en la placa no es una cuestión trivial. El retraso depende de la longitud, el ancho, el grosor y los ángulos de la pista, el grosor y el material de la tabla, la distancia a las diferentes capas de suelo, la proximidad de las pistas entre sí y muchos otros factores. Sin embargo, la influencia de cada uno de estos factores es bastante pequeña y en frecuencias de interfaz bajas, hasta decenas de megahercios, estas dificultades pueden pasarse por alto. Un cálculo simplificado del retraso de la pista se ve así: la velocidad de propagación de una onda en la lámina se considera igual a la mitad de la velocidad de la luz en el vacío. Convertido, esto da aproximadamente 0,007 ns / mm. El error en esta estimación se compensa con una amplia gama de estimaciones de demora. Para el retraso máximo, consideramos el retraso específico igual a 0.010 ns / mm, y para el mínimo - 0.005 ns / mm.

Hay un matiz más. Los ingenieros de circuitos, al diseñar placas de circuito impreso, intentan estirar las pistas de las interfaces síncronas aproximadamente de la misma manera y mantener sus longitudes iguales. Verifique los datos y las longitudes de las pistas del reloj en su tablero de destino. Lo más probable es que sean casi iguales y el componente de las expresiones (DataTrace - ClkTrace) en la práctica se puede considerar cero.

Si hay un elemento de retardo en la ruta de los datos o fragmentos, también debe tenerse en cuenta. Puede ser un búfer, inversor, convertidor de nivel o aislamiento galvánico. Tales elementos son capaces de introducir un retraso muy grande, decenas de nanosegundos, por lo que deben tratarse con mucho cuidado.

Conclusión

En este artículo, vio las fórmulas que determinan la ejecución de restricciones de tiempo en interfaces síncronas. Al conocer estas fórmulas, puede comprender de qué depende la transferencia de datos exitosa y cómo calcular los límites correctos para el analizador. En el próximo artículo daré un ejemplo de cómo formatear un archivo de restricción de tiempo y usar el analizador.