El artículo fue creado sobre la base de mi propia experiencia de intentos de explicarme este tema a mí mismo, a los estudiantes en formación y a los colegas curiosos para no sumergirme en la jungla académica abstrusa, sino de la manera más simple y transparente posible, en el lenguaje cotidiano. Aprendí a trabajar con FPGA sin estudiar y entrenarme en este tema, y sé por mi propia experiencia lo difícil que es entender algo sin una base teórica en este tema y en los circuitos. Para un criador experimentado, lo anterior es elemental. Pero para algún estudiante de cuarto año, el artículo será útil y ayudará a comprender todas estas holguras, configuraciones y sujeciones.

En el artículo, usaré términos con duplicación de su versión en inglés entre paréntesis. Esto se hace porque no se ha establecido una terminología única, y con la duplicación es más fácil entender qué concepto se está discutiendo y, si es necesario, encontrar información al respecto en fuentes en inglés.

Introducción

Daré una breve introducción en el lenguaje de conceptos simples.

Para que algo funcione en la FPGA, debe cargar (cargar, coser) el archivo de firmware en él, utilizando el programador y la utilidad de firmware. El archivo de firmware es el producto de una compilación CAD de un determinado proyecto: carpetas con archivos, cada uno de los cuales describe algún aspecto del proyecto. En casos simples, el propio usuario describe solo archivos con código fuente, un archivo con pinout y un archivo con restricciones de tiempo. CAD maneja silenciosamente el resto de los archivos. De esta tríada, solo el archivo de restricción de tiempo es formalmente opcional.parte del proyecto. En realidad, si su proyecto no contiene frecuencias superiores a 30-50 MHz, es probable que pueda funcionar de alguna manera sin este archivo. Esta opción es apropiada para la facilidad de crear los primeros proyectos educativos. Sin embargo, si su proyecto de capacitación ya contiene frecuencias de reloj altas y no está equipado con un archivo de restricción de tiempo, lo más probable es que en algún lugar dentro de la FPGA, el procesamiento de datos se interrumpa y no podrá averiguar en qué punto del proyecto. En cuanto al trabajo, no al estudio, se requiere estrictamente la descripción del archivo completo de restricciones . Es su responsabilidad verificar y validar la funcionalidad de su proyecto.

El compilador coloca su proyecto en el chip FPGA, recibe un archivo de conexiones de todos los elementos físicos. El analizador de tiempo utiliza el archivo de conexión para calcular todas las duraciones de las transferencias de datos a la FPGA. Estas duraciones no deben ser infinitamente largas ni demasiado cortas. El archivo de restricciones de tiempo le dice al analizador en qué marco deberían estar estas duraciones. Utilizando los resultados del análisis de tiempo, el desarrollador puede ver en qué partes del proyecto hay un margen en el tiempo, y por lo tanto en la frecuencia, y donde no existe ese margen.

Los sistemas síncronos sincronizan el trabajo de procesamiento de datos utilizando señales de reloj de sincronización, que en la jerga se denominan en breve relojes del reloj inglés.... Los resultados intermedios de las operaciones se almacenan en registros capaces de memorizar el estado en la entrada en el momento de la llegada del borde de la señal de reloj y mantenerlo en la salida hasta el siguiente ciclo de reloj.

Así, los circuitos síncronos consisten en transferencias de datos entre registros ( RTL, lógica de transferencia de registros, transferencia r2r ). Y un aspecto clave del análisis temporal consiste en medir Slack ( holgura ). Esta palabra se traduce literalmente como "reserva de tiempo", "flacidez", pero en el entorno de habla rusa a menudo usan papel de calco del inglés - "holgura". En la transferencia inter-registro, estamos hablando preestablecidos pantalones ( Configuración ) y de retención pantalones ( Hold ).

Transferencia entre registros

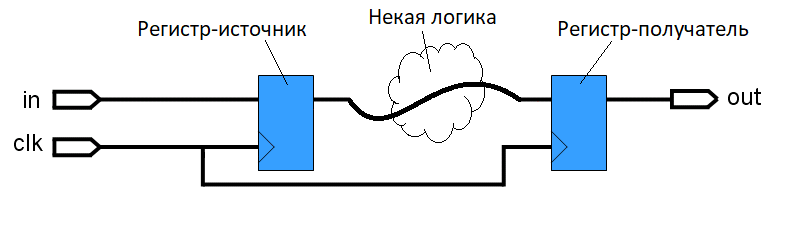

La transferencia entre registros (Fig. 1) se considera como un sistema de dos registros conectados secuencialmente, que operan en relojes síncronos en el caso general. En el caso simple, en una pizca. Un registro desempeña el papel de fuente (fuente) y el otro papel de receptor de datos (destino). Y en la próxima transferencia entre registros, este registro de destinatarios ya se considerará como fuente, etc. Entre los registros en la ruta de datos hay una lógica combinacional arbitraria definida por el usuario. Es asincrónico ya que no tiene elementos de memoria con señal de sincronización, como registros. Esta lógica es ese comportamiento, esas operaciones lógicas que el usuario describe con su código. Los registros son aquellas "variables" de un bit a las que el usuario les da nombres en el código y operan por separado,o combinar en vectores y matrices.

Figura: 1. Esquema de transferencia de datos de un registro a otro

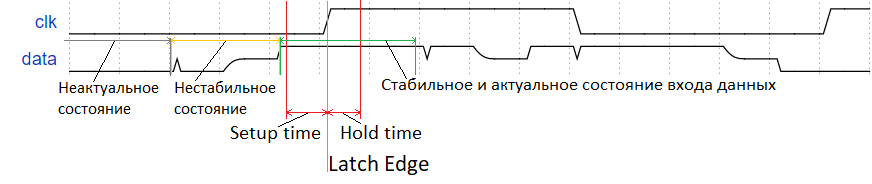

Hay dos conceptos asociados con la recepción de datos por el registro receptor: el tiempo de configuración y los intervalos de tiempo de retención. Describen el intervalo de tiempo durante el cual la señal en la entrada del receptor debe ser estable y relevante. Estable: esencialmente significa que su voltaje debe estar muy cerca de uno de los dos estados lógicos: "0" o "1", y no colgar entre ellos con riesgo de confusión. Relevante: significa que este bit de información debe estar relacionado de manera significativa con este reloj del reloj que lo capturará, y no un bit tardío del reloj anterior.

Tiempo de configuración: tiempo preestablecido, el tiempo mínimo durante el cual antes de la llegada del frente del reloj, la señal de datos ya debería estar establecida en un estado estable.

Tiempo de espera : el tiempo de espera, el tiempo mínimo que después de la llegada del frente del reloj, la señal de datos debe mantenerse en un estado estable.

Es decir, los datos a la entrada del receptor deben ser estables y estar actualizados no solo en el momento de la llegada del frente del reloj, sino también durante un cierto intervalo de tiempo de protección a su alrededor (Fig.2), con una duración de al menos Setup_time + Hold_time. Si se cumple la condición de estabilidad de los datos durante este intervalo, el registro definitivamente podrá capturar los datos entrantes sin errores; de lo contrario, nadie garantiza que no habrá fallas.

Figura: 2.Tiempo de configuración y tiempo de retención como intervalo de protección alrededor del borde de captura en la entrada del reloj del registro

Los valores de tiempo de configuración y tiempo de retención están estrictamente definidos por el fabricante de la FPGA. Dependen de la tecnología de producción del cristal y se consideran constantes para el análisis, lo mismo para cada registro en el cristal. En cualquier caso, estos valores no dependen en modo alguno del usuario, su contabilidad es tarea exclusiva de la utilidad de análisis de tiempos. No es importante para nosotros saber a qué son iguales, es importante para nosotros solo saber que existen y no son iguales a cero.

La esencia del análisis de tiempo es calcular las holguras en el tiempo para cada par de registros en el proyecto, entre los cuales hay transferencia de datos, que los datos deben ser estables durante el intervalo de guarda. Hay muchos pares de r2r en el proyecto, miles o incluso millones, pero cada uno de ellos debe analizarse para asegurarse de que el proyecto funciona.

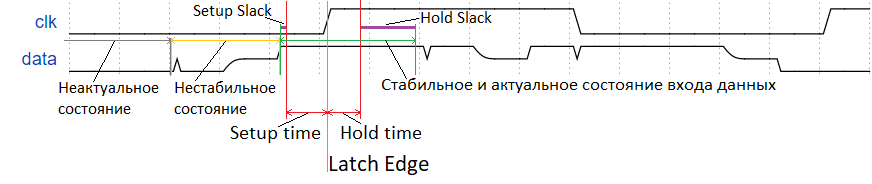

También hay dos holguras, respectivamente: Setup Slack y Hold Slack (Fig. 3).

Setup Slack caracteriza el margen de tiempo que tienen los datos desde el momento de la estabilización hasta el inicio del intervalo de tiempo de Setup.

Hold Slack caracteriza el margen de tiempo que tienen los datos desde el final del intervalo de tiempo Hold hasta la pérdida de estabilidad de los datos.

Los holguras deben ser positivos. Si la holgura es negativa, entonces no se cumple la condición de estabilidad de los datos de entrada y los datos batirán. Cuanto más holgura, mejor, pero debe comprender que en cada registro-destinatario sus holguras preestablecidas y de espera tienen un tiempo común para dos. Esto significa que un aumento en una holgura siempre conduce a una disminución en la otra. Por lo tanto, la mejor opción es cuando ambas holguras son positivas y aproximadamente iguales entre sí, es decir, Se respeta el equilibrio de holguras.

Higo. 3. Holguras positivas, se cumple la condición para la recepción exitosa de datos, pero no hay equilibrio entre las holguras

Cálculo de holgura

Ahora pasemos a cómo se calculan estas holguras. Comencemos con Setup Slack.

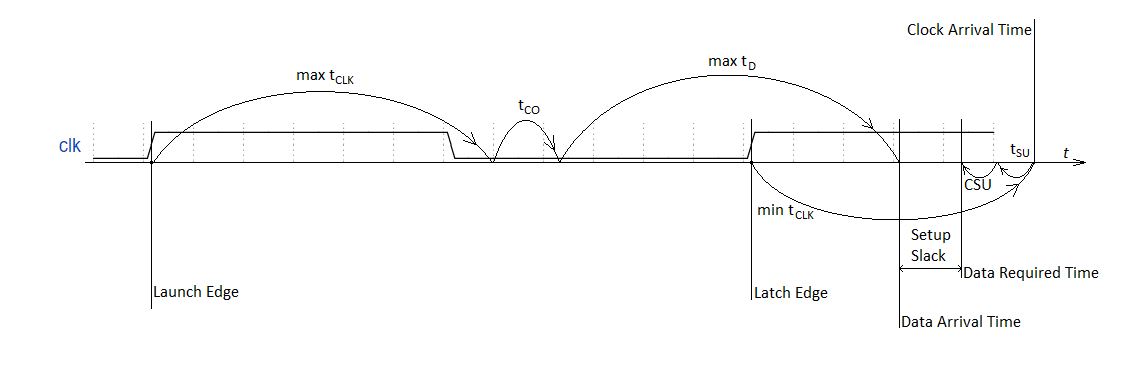

Considere el esquema de transferencia de datos en la Fig. 4.

Fig. 4. Esquema de transferencia de datos

Aquí presentamos conceptos tales como frente de activación, frente de captura, tiempo de llegada de datos, tiempo de espera de datos y tiempo de llegada del reloj.

El Launch Edge es el frente del reloj que llegó a la entrada del registro de origen e inició el proceso de transferencia de datos.

El Latch Edge es el frente de reloj que llega al registro de recepción y lo obliga a capturar datos en la entrada.

El momento de la llegada de los datos ( Hora de llegada de datos ) se define como la llegada real de los datos en el registro de destino.

El tiempo de datos requeridos se define como el tiempo que tardan los datos en llegar al destino antes de la hora preestablecida en el registro de destino.

El tiempo de llegada de un reloj ( Clock Arrival Time ) se define como el tiempo de paso del borde de la captura desde la entrada del reloj de todo el circuito hasta la entrada del reloj del receptor. Además, el frente de captura significa el frente siguiente después del frente de lanzamiento. El frente de lanzamiento permite que los datos pasen de la fuente al destinatario y, después de un período de reloj, el frente de captura captura estos datos del lado del destinatario.

La entrada de reloj de todo el circuito se entiende como un único punto desde donde el reloj diverge hasta todos los registros que operan en él. Suele ser la salida del búfer de reloj global o la salida del PLL. En el caso más primitivo, este es el tramo FPGA, al que está conectado el generador de reloj.

Los términos involucrados en el análisis temporal pueden no tener un valor en puntos, sino un cierto rango de valores posibles, dependiendo de la traza de diseño y la temperatura del cristal. Por tanto, se analiza la peor holgura. Un intercambio de datos se considera exitoso si, incluso en las peores condiciones de holgura, sigue siendo positivo.

¿Cómo se relaciona el momento de la llegada de los datos con el límite de activación?

Consideramos que la llegada de datos pasa a través de una cadena con un registro de algún evento iniciado por un flanco de activación.

El frente de disparo aparece en la entrada del reloj del sistema, luego llega a la entrada del registro fuente por algún tiempo, luego por algún tiempo este registro se dispara y envía nuevos datos a la salida, luego estos datos pasan a través de los circuitos lógicos combinacionales al registro receptor. Se considera la peor y más lenta variante de paso de datos, por lo que los términos vienen con el prefijo "max".

En esta fórmula, el término para el borde de activación tiene el significado del punto de referencia relativo al desarrollo de los eventos, y no un valor medido en nanosegundos.

TérminoEs el tiempo máximo que tarda el flanco de disparo en pasar de la entrada de reloj de todo el circuito a la entrada de reloj de la fuente. Como regla general, el analizador simplemente toma el rango de tiempo de “exactamente no menos que” a “exactamente no más que” y sustituye el límite superior “definitivamente no más que” en esta fórmula. Este valor es independiente del usuario. El compilador decide por sí mismo dónde colocar el registro en el cristal y tiene en cuenta el tiempo que tarda el reloj en viajar hasta él. La red de conexiones a través de la cual la señal de reloj diverge del búfer de reloj global a los registros está diseñada para que la señal de reloj llegue a cualquier registro en casi la misma cantidad de tiempo. Por tanto, de hecho, la diferencia entre y extremadamente pequeña, pero aún tenida en cuenta.

Término- este es el tiempo de reloj a salida , que el registro gasta en ver el borde en la entrada del reloj para cambiar los datos en su salida. El analizador considera que este valor es igual para todos los registros del chip. Este valor es independiente del usuario.

El ultimo trimestreEs el tiempo máximo que tarda un evento (datos) en pasar por la lógica de combinación entre registros, que es definida por el usuario. Este valor depende en gran medida del usuario. Expresa la cantidad de lógica combinacional entre registros. A su vez, las largas cadenas de lógica combinacional son a menudo el resultado de una codificación inexacta por parte del usuario.

El momento en que el fragmento llega al destinatario es más fácil de calcular:

Este es el momento más temprano en el que el borde de captura alcanza la entrada de reloj del registro de recepción.

Término- este es el tiempo mínimo durante el cual el frente de captura llegará a la entrada del reloj del destinatario, es decir, por analogía con la fórmula anterior, este tiempo es “definitivamente no menor que”. El guión en este caso significa que estamos hablando de la entrada de reloj del receptor, no de la fuente.

El tiempo de espera para los datos se define como el tiempo que tardan los datos en llegar al receptor antes del tiempo preestablecido en el registro del receptor:

Término - esto ya lo conocemos el tiempo de configuración, que se considera el mismo para cada registro en el cristal. Esta vez es independiente del usuario.

TérminoEs la incertidumbre de la configuración del reloj , la incertidumbre del tiempo preestablecido. Como cualquier otra incertidumbre en el análisis temporal de la CSU no es un proceso físico, sino una forma de reflejar el efecto del jitter en el análisis, o simplemente una forma de introducir un tiempo de guardia en el análisis por si acaso. En pocas palabras, se trata de una reserva de tiempo para tener en cuenta procesos difíciles.

Ahora que estos términos están definidos, podemos definir una holgura preestablecida como la diferencia más pequeña entre el tiempo que se permite viajar al destino y el tiempo que realmente toma.

Ahora ampliemos estos términos y reorganicemos un poco:

Aquí han aparecido nuevos términos.

Está claro sobre el período, este es el período de la frecuencia del reloj, es decir tiempo entre Launch Edge y Latch Edge.

Término- este es el reloj sesgado - el valor mínimo de la extensión del tiempo de llegada de un flanco de reloj desde la entrada de reloj del sistema a diferentes registros síncronos. La extensión de reloj mínima se define como la diferencia entre el retraso de reloj más pequeño para el receptor y el retraso de reloj más grande para la fuente.... El analizador no hace ninguna diferencia al estimar este tiempo para diferentes registros en el chip.

Así es como calculamos la holgura preestablecida. Un margen positivo es bueno, un margen negativo es malo. La holgura se traduce literalmente en flacidez. Entonces, si hay una holgura, entonces la transferencia entre registros no está configurada "vnatyag", el "hilo" condicional se hunde libremente. La holgura es negativa: significa que el hilo de la transmisión se detuvo y se rompió.

La Figura 5 muestra cómo se puede representar gráficamente la fórmula de holgura:

Fig. 5. Representación gráfica de la expresión de holgura de configuración

Muestra la relación en el fondo de la señal de reloj, y esta es la señal de reloj en la entrada de reloj del sistema y no en la entrada de ninguno de los registros.

Ahora calculemos la holgura de retención de manera similar .

También se puede representar mediante una expresión en la que los términos hayan cambiado de signo:

Estos términos ahora se consideran desde el otro lado.

Ahora se considera aquí la variante más rápida de paso de datos y donde "max" era "min".

El momento de llegada del clok front también se ve de otra manera, como el último posible:

Es importante tener en cuenta que en el caso de Hold Slack, los frentes de Launch Edge y Latch Edge ahora son uno y el mismo frente, en lugar de dos frentes diferentes separados por el período de reloj. En esta situación, el registro de destinatarios necesita tener tiempo para retener los datos en la entrada durante el tiempo de retención desde la llegada del frente del reloj. Pero los datos se modifican en su entrada por el mismo frente, que vino en algún otro lugar del registro fuente. Por tanto, en el análisis de la holgura de retención, la diferencia eses cero, no punto.

El tiempo requerido en este caso se define como el tiempo durante el cual los datos no deben cambiar en la entrada de los datos del destinatario, para no atrapar el tiempo de espera:

Término - esto ya lo conocemos. Tiempo de espera, el tiempo de espera. Se considera igual para todos los registros del chip y no depende del usuario.

TérminoEs la incertidumbre de retención del reloj , la incertidumbre del tiempo de retención. En general, tiene el mismo significado que CSU y, por regla general, se le considera igual.

Si, como en el caso de la holgura preestablecida, expande los términos y los intercambia, entonces la expresión de holgura de retención se puede transformar en la siguiente forma:

Otro vistazo a esta fórmula

Arriba, se presentó un método para calcular holguras, que es característico de la comprensión humana de los procesos que tienen lugar. Aquí "viene el frente ...", "vienen los datos ...". Si te interesa, como complemento, te cuento cómo el analizador de limitaciones de tiempo imagina estos cálculos.

El analizador agrupa los términos de manera diferente, según las razones de su máquina. Pero al final llega el mismo resultado.

Utiliza los términos Relación de configuración del reloj ( SR ) y Relación de retención del reloj ( HR ), que se pueden traducir como la relación del tiempo entre los bordes del disparador para preajuste y retención, respectivamente.

La figura 6 muestra cómo se relacionan estos frentes:

Fig. 6. Frentes utilizados en los cálculos de holgura.

Puede convertir inmediatamente las expresiones resultantes en una forma más comprensible:

El tiempo entre registros más largo (se requiere r2r más grande) es el tiempo máximo disponible para que los datos lleguen al destino antes del inicio del intervalo preestablecido:

El retardo entre registros más largo (retardo r2r más largo) es el tiempo que se tarda en transferir datos desde el registro de origen al registro de destino a lo largo de la ruta más larga:

Ahora podemos definir la holgura preestablecida como la diferencia entre el tiempo disponible para llegar al registro de destino y el tiempo real para llegar allí:

Expandir los términos de esta fórmula nos dará la representación familiar de la holgura preestablecida:

Ahora sobre la holgura de retención. El requisito r2r más pequeño es el tiempo necesario para almacenar datos en la entrada del registro de destino:

Retardo entre registros más corto:

Ahora definimos la holgura del preset como la diferencia entre el tiempo más rápido para que los datos salgan de la entrada del receptor y el tiempo que lleva mantenerlos allí:

Al expandir los términos, la expresión también adquiere la forma ya familiar:

¿Qué conclusiones se pueden sacar de fórmulas aburridas?

Hemos visto cómo se calculan las holguras. ¿Cómo utilizar este conocimiento?

Veamos las expresiones flojas nuevamente:

Si algunas holguras del proyecto se vuelven negativas, podemos cambiarlas cambiando sus términos. Es decir, vemos cómo podemos arreglar los problemas.

Vemos términos que no dependen del usuario, sino que dependen únicamente de la tecnología de cristal. eso... No hay forma de interferir.

Vemos los términos CSU y CHU, que el analizador suele tomar como el parámetro CU - Incertidumbre del reloj, la inestabilidad de la frecuencia del reloj. En términos generales, este parámetro es pequeño, decenas de picosegundos. Lo especifica el usuario en el archivo de restricciones. Y el usuario, a su vez, lo toma de la especificación del generador de reloj. Se considera que un búfer de reloj o FPGA PLL interno, que recibe un reloj externo del oscilador y lo convierte en un reloj interno en la entrada del reloj del sistema, mantiene el valor de CU igual al recibido del oscilador. Si no se especifica CU, el analizador lo establecerá en algún valor predeterminado, por ejemplo, Quartus lo establece en 20 ps. En el caso general, este término nos dice que es mejor usar osciladores altamente estables con una pequeña cantidad de inestabilidad para sincronizar. Los buenos osciladores son del orden de 20 a 60 ps.

El término de período muestra que la forma obvia de combatir el desvío de la transmisión de datos es reducir la frecuencia del reloj. Es razonable, pero no siempre aceptable, ya que los términos de referencia suelen requerir cierto rendimiento del sistema, por debajo del cual es imposible ir por debajo. Y el rendimiento depende directamente de la frecuencia del reloj. También podemos ver la diferencia entre la holgura preestablecida y de retención: la holgura de retención es independiente de la frecuencia.

Y finalmente, el términoesencialmente caracteriza la eficiencia del código escrito. Por lo tanto, la forma principal de resolver los problemas de holgura es reescribirlo correctamente. Gran momentoaparece en diseños de hardware demasiado complejos que requieren demasiada lógica de combinación. Si tiene construcciones tan complejas en su proyecto, entonces la forma clásica de resolver el problema es dividir una transferencia compleja r2r en varias simples insertando otros 1-2 registros en la secuencia de operaciones. En este caso, el retraso en ciclos para la operación aumentará, pero la velocidad de operación aumentará. Por ejemplo, agregar varios vectores en un ciclo de reloj no es una buena idea. Es mejor sumar varios vectores sucesivamente, con sumas intermedias. A veces es imposible dividir algunas construcciones complejas en una tubería de varias simples; entonces dicha lógica debe reescribirse de alguna manera fundamentalmente diferente.

Conclusión

El objetivo de este artículo es conocer la existencia del concepto de holgura y de qué depende físicamente esta holgura. Sabiendo esto, puede estudiar de forma independiente los informes del analizador de limitaciones de tiempo, sacar conclusiones y depurar el rendimiento de su proyecto. Son fórmulas con las que casi nunca tendrás que hacer un cálculo real. Ni siquiera necesitas recordarlos de memoria. Solo es importante comprender la lógica de lo que está sucediendo en la transferencia entre registros y comprender qué factores determinan la velocidad del proyecto.